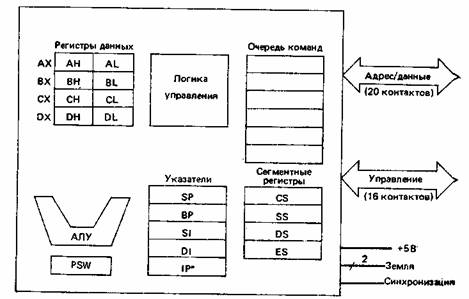

Внутренняя

архитектура микропроцессора 8086 представлена на Рис. 7.8. За исключением

регистра команд, которым фактически служит 6-байтная очередь, регистры

управления и рабочие регистры разделены на три группы в соответствии с

выполняемыми ими функциям. Имеются группа регистров данных, представляющая

собой, по существу, набор арифметических регистров; указательная группа,

содержащая базовые и индексные, регистры, а также программный счетчик и

указатель стека, и сегментная группа, в состав которой входят специальные

базовые регистры. Все регистры имеют длину 16 бит.

Рис. 7.5. Внутренняя конфигурация

микропроцессора 8086

В

группу регистров данных входят регистры АХ, ВХ, СХ и DX. Они предназначены для

хранения операндов и результатов операций и допускают адресацию не только целых

регистров, но и их младшей и старшей половин. Например, допускается

использовать два байта в регистре АХ вместе, а также указывать отдельные байты

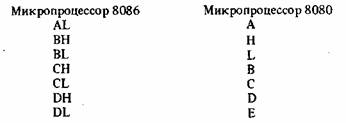

AL (младший) и АН (старший). С точки зрения программной совместимости с

микропроцессором 8080 имеется следующее соответствие:

Регистры

ВХ, СХ и DX кроме арифметических функций имеют и специальные назначения:

ВХ

служит базовым регистром в вычислениях адреса,

СХ

в некоторых командах выступает неявным счетчиком,

DX

в некоторых операциях ввода-вывода содержит адрес порта ввода-вывода.

Указательная

и индексная группы представлены регистрами IP, SP, ВР, SI и DI.

Указатель команды IP и регистр SP фактически являются программным счетчиком и

указателем стека, но полные адреса команды и стека образуются суммированием

содержимого этих регистров и содержимого сегментных регистров CS и SS, которые

рассматриваются далее. Регистр ВР является базовым при обращении к стеку и

может использоваться с другими регистрами и (или) смещением, которое является

частью команды. Регистры SI и DI предназначены для индексирования. Хотя их

можно использовать сами по себе, они часто комбинируются с регистрами ВХ и ВР и

(или) смещением. За исключением регистра IP, любой из указателей может хранить

операнд, но допускает обращения только к 16-битному регистру.

Чтобы

обеспечить гибкую базовую адресацию и индексирование, адрес данных формируют

путем сложения содержимого регистров ВХ или ВР, содержимого регистров SI или DI

и смещения. Результат вычислений адреса называется эффективным адресом ЕА или

смещением. (В руководствах фирмы Intel термин "эффективный адрес"

применяется в контексте машинного языка, а термин "смещение"

(offset)— в контексте языка ассемблера. Слово "смещение"

(displacement) означает величину, которая прибавляется к содержимому

регистра(ов) для образования ЕА.) Однако окончательный адрес данных

определяется ЕА и соответствующим сегментным регистром — DS, ES или SS.

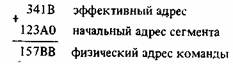

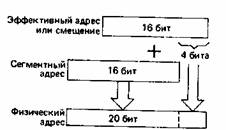

Сегментную

группу образуют регистры CS, SS, DS и ES. Как говорилось ранее, участвующие в

формировании адреса регистры ВХ, IP, SP, ВР, SI и DI имеют длину всего 16 бит,

поэтому эффективный адрес имеет такую же длину. Но, с другой стороны,

выдаваемый на шину адреса физический адрес должен содержать 20 бит.

Дополнительные 4 бита образуются при сложении эффективного адреса с содержимым

одного из сегментных регистров, как показано на Рис. 7.6. Перед сложением к

содержимому сегментного регистра справа добавляются четыре нуля, что дает

20-битный результат. Если, например, (CS) = 123А и (IP) = 341В, следующая

команда будет выбираться по адресу 157ВВ:

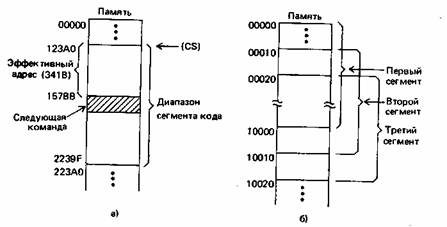

Рис. 7.6. Формирование физического

адреса

(Отметим,

что круглые скобки подразумевают слово "содержимое", например запись

(IP) означает содержимое IP. Кроме того, все адреса даются в 16-ричной

системе.)

Рис. 7.7. Вычисление адреса (а) и

сегментация памяти (б)

Применение

сегментных регистров, по существу, разделяет пространство памятника

перекрывающиеся сегменты, каждый из которых имеет размер 64К байт и начинается

на 16-байтной границе (называемой границей параграфа), т. е. начинается с

адреса, кратного 16. Далее мы будем называть содержимое сегментного регистра

сегментным адресом, а сегментный адрес, умноженный на 16, - начальным

физическим сегментным адресом или просто начальным сегментным адресом.

Иллюстрацией рассмотренного примера служит Рис. 7.7, а, а общий принцип сегментации

памяти показан на Рис. 7.7, б.

Наличие

сегментных регистров обеспечивает следующие преимущества:

емкость

памяти может доходить до 1М байт, хотя команды оперируют 16-битными адресами;

секции

кода, данных и стека могут иметь длину более 64К байт благодаря использованию

нескольких сегментов кода, данных или стека;

упрощается

использование отдельных областей памяти для программы, ее данных и стека;

при

каждом выполнении программы она сама и (или) ее данные могут размещаться в

различных областях памяти.

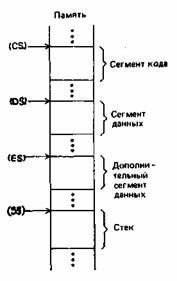

На

Рис. 7.8 показано, каким образом можно распределить в памяти программный код,

данные и стек. Самый простой и удобный вариант - разместить код и данные в

единой области памяти, а стек - в некоторой фиксированной области, которая

начинается, например, с адреса 08000. Такое решение приемлемо, когда в памяти

всегда находится только одна программа, но в мультипрограммной среде в памяти

одновременно находятся несколько программ. При мультипрограммировании лучше

всего делать смежные блоки памяти как можно меньше, поэтому выгоднее отделить

код от данных. Вариант смежного размещения кода и данных существует всегда, так

как в регистры CS, DS и ES всегда можно загрузить одно и то же содержимое.

Рис. 7.8. Распределение кода

программы, ее данных и стека

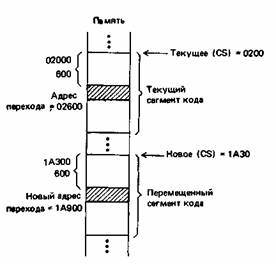

Рис. 7.9. Перемещение программы с

помощью регистра CS

Четвертое

преимущество также связано с мультипрограммированием. Рассмотрим, например,

систему с разделением времени, в которой несколько пользователей выполняют

различные программы.

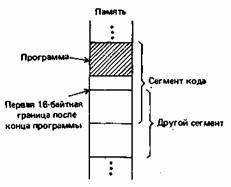

Рис. 7.10. Перекрывающиеся сегменты

Если

в памяти места недостаточно, приходится обменивать программы между основной

памятью и внешней. Следовательно, программы динамически размещаются в различных

областях памяти. Например, при данном выполнении программа может начинаться с

физического адреса 02000, а при следующей загрузке в память она может

начинаться с адреса 1АЗОО. Возникает вопрос: если в программе есть команда

перехода, которая при данном выполнении вызывает переход но адресу 02600, будет

ли осуществлен правильный переход по адресу 1А900, когда программа перемещается

в область с начальным адресом 1АЗОО? Ответ оказывается утвердительным, если при

перемещении программы изменить содержимое CS на 1АЗОО. Такая ситуация отражена

на Рис. 7.9. Аналогичные утверждения относятся и к перемещению блоков данных

или стека.

Хотя

сегменты имеют длину 64К байт, для лучшего использования памяти они могут

перекрываться. Если, как показано на Рис. 7.10, программа занимает только часть

сегмента, то другой сегмент кода, данных или стека может перекрываться

сегментом программы и начальный адрес второго сегмента может находиться в

пределах 16 байт от конца программы. Могут "пропасть" только

несколько байт между концом программы и следующей 16-байтной границей.

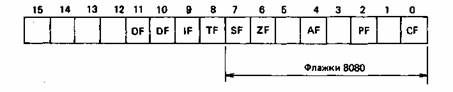

Слово

состояния процессора PSW микропроцессора 8086 содержит 16 бит, но семь из них

не используются. Флажки микропроцессора (см. Рис. 7.11) 8086 разделяются на

условные (или флажки условий), отражающие результат предыдущей операции АЛУ, к

управляющие (или флажки управления), от которых зависит выполнение специальных

функций. Младший байт в PSW соответствует 8-битному PSW микропроцессора 8080 и

содержит все флажки условий, кроме OF.

Рис. 7.11. Слово состояния

микропроцессора 8086

Флажками

условий являются:

Флажок

знака SF. Равен старшему биту результата. Так как в дополнительном коде старший

бит отрицательных чисел содержит 1, а у положительных чисел он равен 0, флажок

SF показывает знак предыдущего результата.

Флажок

нуля ZF. Устанавливается в 1 при получении нулевого результата и сбрасывается в

0, если результат отличается от нуля.

Флажок

паритета PF. Устанавливается в 1, если младшие 8 бит результата содержат четное

число единиц; в противном случае он сбрасывается в 0.

Флажок

переноса CF. При сложении (вычитании) устанавливается в 1, если возникает

перенос (заем) из старшего бита. Другие команды также воздействуют на этот

флажок, что будет отмечено при их обсуждении.

Флажок

вспомогательного переноса AF. Устанавливается в 1, если при сложении

(вычитании) возникает перенос (заем) из бита 3. Флажок предназначен только для

двоично-десятичной арифметики.

Флажок

переполнения OF. Устанавливается в 1, если возникает переполнение, т. е.

получение результата вне допустимого диапазона. При сложении этот флажок

устанавливается, если имеется перенос в старший бит и нет переноса из старшего

бита или наоборот. При вычитании он устанавливается, когда возникает заем из

старшего бита, но заем в старший бит отсутствует, или наоборот.

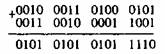

Тогда

после ее выполнения получаются такие состояния флажков:

![]()

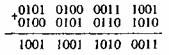

Если

в предыдущей команде выполнялось сложение

флажки

принимают следующие состояния:

![]()

Пусть,

например, предыдущая команда производила следующее сложение:

Флажки

управления микропроцессора 8086:

Флажок

направления DF. Применяется в командах манипуляций цепочками. Если он сброшен,

цепочка обрабатывается с первого элемента, имеющего наименьший адрес. В

противном случае цепочка обрабатывается от наибольшего адреса к наименьшему.

Флажок

разрешения прерываний IF. Когда установлен этот флажок, ЦП распознает

маскируемые прерывания; в противном случае эти прерывания игнорируются

(подробнее см. гл. 4 и 6).

Флажок

прослеживания (трассировки) TF. Когда этот флажок установлен, после выполнения

каждой команды генерируется внутреннее прерывание (см. гл. 4).