7.1.4. Внутренние

операции микропроцессора

В

общем виде действия компьютера включают в себя следующие шаги :

1)

Выборка следующей команды по адресу из PC.

2)

Загрузка ее в регистр команды и дешифрирование с одновременным инкрементом PC для

адресации следующей по порядку команды.

3)

Выполнение команды, а в случае перехода загрузка в PC адреса перехода.

4)

Повторение шагов 1—3.

Действия

микропроцессора 8086 соответствуют этому общему шаблону, но имеются некоторые

различия и совмещение нескольких операций.

Адрес

следующей команды равен сумме (IP) и (CS) х 1610, а регистр команды

представлен 6-байтной очередью FIFO ("первый пришел - первый ушел"),

которая непрерывно заполняется, когда системная шина не требуется для других

операций. Такое "опережение" значительно увеличивает пропускную

способность ЦП, так как к моменту завершения текущей команды следующая команда

чаще всего уже находится в ЦП.

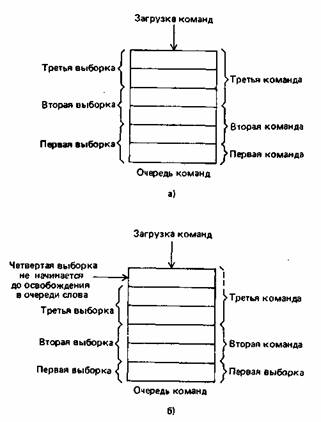

Рис. 7.12. Заполнение очереди команд после

перехода, когда первая команда имеет четный (а) и нечетный (б) адрес

В

случае перехода очередь сбрасывается и не дает экономии времени, но в среднем

это происходит нечасто. Чтобы показать эффект опережающей загрузки очереди,

рассмотрим команду 8-битного умножения. Эта команда выполняется минимум 71 такт

синхронизации, но для считывания слова из памяти требуется всего 4 такта.

Следовательно, при выполнении команды оказывается много тактов синхронизации,

во время которых шина свободна для заполнения очереди команд. Хотя

микропроцессор 8086 может обращаться к слову по любому адресу, при нечетном

адресе требуются два обращения к памяти: для младшего и для старшего байтов.

Следовательно, возможна некоторая экономия времени, если хранить слова только

по четным адресам. Длина команд составляет от одного до шести байт, но очередь

позволяет считывать команды словами по четным адресам. Имеется только одно

исключение, связанное с переходом по нечетному адресу. В этом случае ЦП

считывает сначала один байт, а затем продолжает считывать снова по четным

адресам. На Рис. 7.12, а показано заполнение очереди такой последовательностью

команд: 1-байтная команда, 2-байтная команда и 3-байтная команда.

Предполагается, что эта последовательность начинается по четному адресу. На

Рис. 7.12, б показана эта же последовательность, но начинающаяся по нечетному

адресу. Отметим, что во втором случае последний байт третьей команды не

передается в очередь до тех пор, пока в ней не образуется пустое слово.