7.4.5.1. Интерфейс с локальной

магистралью

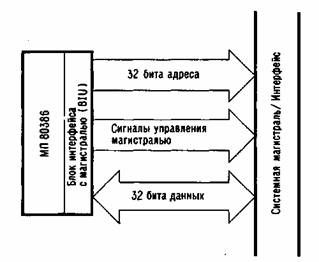

Магистраль-это путь, по которому передаются данные от

любого из нескольких источников

к любому из нескольких приемников. Она работает как общий канал связи между рядом блоков, такими

как процессор, память и периферийные устройства. На рис. 5.1 показана структурная схема интерфейса

с общей магистралью.

Процессор выполняет множество магистральных операций в

ответ как на внутренние,

так и внешние запросы, например на требования обслуживания по прерыванию. Он обменивается

информацией с внешней памятью, устройствами ввода-вывода и другими устройствами через интерфейс

с параллельной магистралью.

Этот интерфейс организуется с помощью двунаправленной шины данных, отдельной шины адреса, пяти

сигналов состояния магистрали и трех сигналов управления магистралью. Работа происходит следующим

образом.

Двунаправленная шина данных. Имеются 32 вывода (D31-DO), по

которым за один раз

могут передаваться 8, 16, 24 или 32 бит.

Шина

адреса. Эта шина генерирует

32-разрядные адреса и состоит из 30 выводов адреса

(А31-А2) и четырех выводов выбора байтов (ВЕЗ#-ВЕО#). Каждый из выводов выбора байтов соответствует одному из

передаваемых байтов 32-разрядной шины

данных. Выводы адреса идентифицируют область из 4 байтов. Выводы выбора байтов выбирают активные байты внутри этой

области.

Состояние магистрали. Эти выводы устанавливают тип выполняемого цикла магистрали и показывают

следующие условия:

сигнал LOCK #-блокированный цикл магистрали;

состояние адреса (ADS #)-выходы шины адреса

достоверны;

данные/управление (В/С#)-цикл данных или управления;

память/ввод-вывод (МДО)-цикл памяти или ввода-вывода;

запись/чтение (\\7К#)-цикл записи или чтения.

Управление магистралью. Эти выводы позволяют внешней

логике управлять циклом

магистрали на основе принципа «цикл за циклом». Назначение входов:

сигнал READY # -завершает текущий цикл

магистрали;

следующий адрес (NA#)-3TOT вывод позволяет организовать

конвейер

Рис. 5.1. Общий

интерфейс с магистралью.

адресов, т. е. сигнал на этом выводе заставляет

процессор генерировать сигналы адреса и состояния для следующего цикла магистрали в

текущем цикле;

3) 16-разрядная шина данных (BS16#)-активизация этого вывода

говорит о том, что

ширина магистрали составляет 16 разрядов и будет передано 16 бит информации. Данные передаются по

младшим 16 бит шины данных. Передача более 16 бит обеспечивается дополнительными циклами

магистрали.

Следующие семь выводов управляют выполнением команд в МП

80386 и интерфейсом

с внешними задатчиками магистрали. Процессор обеспечивает как стандартный интерфейс для взаимодействия с другими

задатчиками магистрали, так и поддержку

специального интерфейса с арифметическим сопроцессором.

RESET. Этот вход используется для

установки МП 80386 в начальное состояние.

INTR

(маскируемое прерывание) и NMI

(немаскируемое прерывание). Эти входы служат

для прерывания выполнения текущего потока команд процессором иинициирования

выполнения программы обработки прерывания.

CLK2. На этот вход поступает сигнал

двойной тактовой частоты для синхронных операций. При тактовой частоте 16 МГц МП 80386 использует

сигнал32 МГц CLK2, т. е. сигнал CLK внутри процессора делится на

два, так что тактовая частота МП 80386 составляет половину от частоты сигнала CLK2.

BUSY#, ERROR # и PEREQ (запрос

сопроцессора). Эти сигналы образуют интерфейс

с внешним арифметическим сопроцессором. Сигналы ERROR # иBUSY# являются сигналами состояния,

поступающими от сопроцессора. СигналPEREQ позволяет сопроцессору

запрашивать данные от МП 80386.

HOLD.

Этот сигнал может генерироваться другим задатчиком магистрали как требование к МП 80386 передать управление

магистралью. При передаче управления

локальной магистралью МП 80386 активирует сигнал HLDA

(подтверждение

захвата).

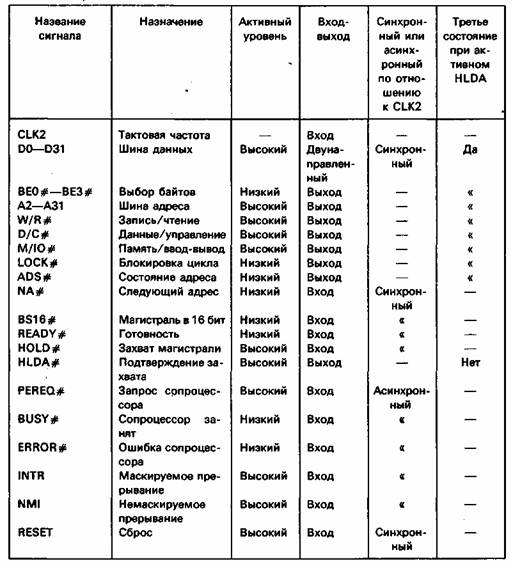

На рис. 5.2 показано назначение сигнальных выводов МП

80386. Полный список выводов МП 80386

приведен в гл. 7.

Существуют семь типов магистральных операций: чтение

памяти, запись в память,

чтение ввода-вывода, запись в ввод-вывод, выборка команды, подтверждение прерывания и состояние останова.

Рис. 5.2. Назначение

сигнальных выводов МП 80386.

Каждый цикл магистрали начинается, когда на шине адреса

присутствует достоверный адрес и выводы состояния магистрали установлены в те

состояния, которые

соответствуют типу цикла магистрали. Циклы чтения и записи в память могут быть заблокированы для

предотвращения использования локальной магистрали другим задатчиком, а также для обеспечения

целостности операций «чтение -модификация-запись».

(Более подробная информация по задатчикам/исполнителям магистрали MULTIBUS содержится в гл. 12 и приложении

4.)

Конвейер адресов позволяет циклам магистрали

перекрываться по времени, что увеличивает интервал времени, отводимый памяти или устройствам

ввода-вывода для

отклика. Первый цикл после незанятого состояния магистрали никогда не

конвейеризуется. Для инициализации конвейера адресов

этот цикл должен быть расширен по крайней мере на один такт CLK так,

чтобы сигналы адреса и состояния могли быть выведены перед завершением цикла.

Последующие циклы могут быть конвейеризованы до тех пор, пока не встретится незанятый цикл магистрали.