7.1.8. Время

выполнения команд

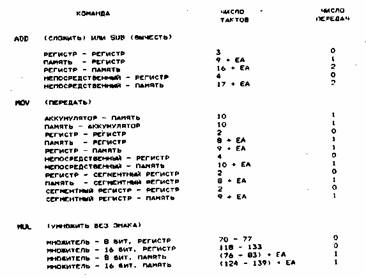

Время

выполнения команды можно определить, умножая число тактов синхронизации,

необходимых для выполнения команды, на период синхронизации. Это время можно выразить

в виде суммы базового времени выполнения (которое зависит от команды и режима

адресации) и времени вычисления эффективного адреса, если привлекается операнд

из памяти. Базовое время выполнения предполагает, что выполняемая команда уже

выбрана и находится в очереди команд; в противном случае требуется учесть

дополнительные такты синхронизации, необходимые для выборки команды. Базовые

времена выполнения некоторых типичных команд микропроцессоров 8086/8088

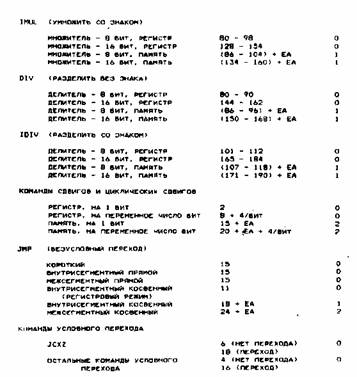

приведены на Рис. 7.24, а полная информация содержится в приложении. Время

вычисления эффективного адреса зависит от режима адресации, что показано на

рис.2.22.

Третий

столбец на Рис. 7.24 показывает число обращений к памяти, необходимых для

выполнения команд. Чтобы определить время выполнения команды, в которой

осуществляется обращение к полному слову памяти, следует учесть выравнивание

операнда. Если слово имеет нечетный адрес, микропроцессор 8086 считывает его за

два цикла шины, длящихся по 4 такта синхронизации. Следовательно, каждое

обращение к слову с нечетным адресом требует 4 дополнительных такта

синхронизации. В микропроцессоре 8088 на передачу каждого слова необходимо

прибавить 4 такта синхронизации, так как в цикле шины передается только один

байт.

Рис. 7.24. Времена выполнений

некоторых команд

Рис. 7.25. Время, необходимое для

вычисления эффективного адреса

Отметим,

что некоторые команды имеют несколько отличающихся базовых времен выполнения в

зависимости от режимов адресации. Примеры на Рис. 7.24 показывают, что для

данной двухоперандной команды операция регистр-— регистр выполняется быстрее,

чем с остальными режимами адресации, а операция регистр - память выполняется

медленнее операции память — регистр из-за дополнительного времени на

запоминание результата в памяти. Базовое время выполнения некоторых команд

зависит также от данных. Типичными примерами служат команды умножения, деления,

сдвига и циклического сдвига. Для команд условного перехода приведено два

времени — меньшее соответствует случаю, когда условие не удовлетворяется и переход

не производится, а большее соответствует реализации перехода. Во втором случае

учитывается нарушение очереди команд и выборка следующей команды.

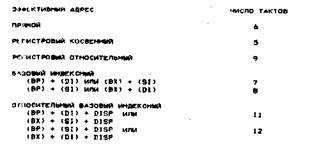

Пусть

частота синхронизации равна 5 МГц (период 0,2 мкс). Тогда времена выполнения

различных форм команды ADD вычисляются следующим образом.

Сложение

регистр — регистр (результат в регистре) требует трех тактов синхронизации (0,6

мкс) для операнда байта или слова.

Сложение

память - регистр (результат в регистре) с использованием относительной базовой

индексной адресации требует

9

(базовое) + 12 (вычисление адреса) =21 такт синхронизации (4,2 мкс)

для

операции над байтами или словами, причем слово находится по четному адресу, или

9

+ 12 + 4 (дополнительные такты) = 25 тактов (5,0 мкс).

если

слово находится по нечетному адресу.

Сложение

регистр - память (результат в памяти) с использованием базо- ' вой индексной

адресации требует

16

(базовое) + 8 (вычисление адреса) = 24 такта синхронизации (4,8 мкс)

для

операции над байтами или словами, причем слово находится по четному адресу, или

16

+ 8 + 4 (считывание слова) + 4 (запоминание слова) = 32 такта синхронизации

(6,4 мкс),

если

слово находится по нечетному адресу.