Несколько

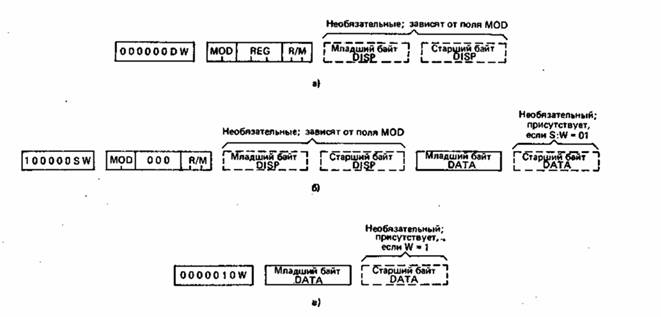

типичных форматов команд микропроцессора 8086 приведены на Рис. 7.16. Длина

команд варьируется от одного до 6 байт. Длина смещений и непосредственных

данных может быть 8 или 16 бит в зависимости от команды. В первых одном или

двух байтах команды находятся код операции и указание режима адресации. После

них могут находиться:

ни

одного дополнительного байта;

двухбайтный

ЕА (только для прямой адресации);

одно-

или двухбайтное смещение;

одно-

или двухбайтный непосредственный операнд;

одно-

или двухбайтное смещение с последующим одно- или двухбайтным непосредственным

операндом;

двухбайтное

смещение и двухбайтный сегментный адрес (только для прямой межсегментной

адресации).

Рис. 7.16. Примеры форматов команд

микропроцессора 8086

Применение

одной из перечисленных возможностей определяется кодом операции и режимом

адресации. Если длина смещения или непосредственного операнда составляет два

байта, первым всегда следует младший байт.

Обычно

код операции занимает первый байт команды, но в некоторых командах в первом же

байте указывается регистр, а в нескольких других командах три бита кода

операции находятся во втором байте. В большинстве кодов операций имеются

следующие однобитные индикаторы:

Бит

W. Если команда может оперировать

байтом и словом, в коде операции имеется бит W, который определяет операцию с

байтом ( W = 0) или словом (W=l).

Бит

D. Содержится в двухоперандных

командах (за исключением команд с непосредственным операндом и цепочечных

команд, которые рассматриваются в гл. 5). Одним из операндов должен быть

регистр, определяемый полем REG. В таких командах бит D показывает, чем

является регистр: операндом-источником (D = 0) или операндом-получателем (D =

1).

Бит

S. 8-битное число в дополнительном

коде можно расширить до 16-битного в дополнительном коде, если сделать все биты

старшего байта равными старшему биту младшего байта. Такая операция называется

расширением знака (или расширением со знаком). Бит S появляется вместе с битом

W в командах сложения, вычитания и сравнения с непосредственным операндом и

расшифровывается следующим образом:

8-битная

операция — S:W = 00;

16-битная

операция с 16-битным непосредственным операндом- S:W = 01; 16-битная операция с

8-битным операндом, который расширяется со знаком до 16 бит, - S:W =11.

При

небольших числах последний вариант допускает использовать однобайтный

непосредственный операнд.

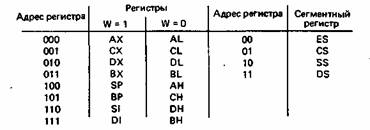

Рис. 7.17. Адреса регистров

Бит

V. Применяется в командах сдвигов

для определения числа сдвигов.

Бит

Z. Используется в команде REP.

Сегментный

регистр определяется двумя битами, а любой другой регистр — тремя. Адреса

регистров (т.е. двоичные обозначения их) приведены на Рис. 7.17.

Неоднозначности использования, например, 00 для указания сегментного регистра

ES и 000 для указания регистров АХ и AL не возникает, так как нужный регистр

подразумевается кодом операции.

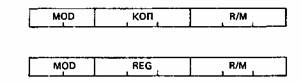

Если

на код операции и режим адресации отводятся два байта, второй байт имеет одну

из следующих двух форм:

Первая

из них предназначена для однооперандных команд (или двухоперандных, в которых

один из операндов неявно определяется кодом операции) . Вторая форма характерна

для двухоперандных команд, причем поле REG определяет регистр, который в

зависимости от значения бита D является операндом-источником или

операндом-получателем.

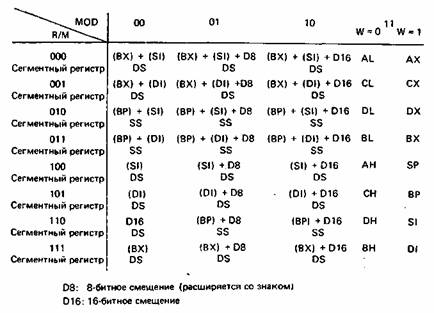

Операнд,

указываемый полями MOD и R/M, определяется в соответствии с таблицей,

приведенной на Рис. 7.18. Если MOD ≠ 11, эффективный адрес вычисляется

согласно таблице. Отметим, что MOD = 00 означает отсутствие смещения, за

исключением случая R/M = 110, который обозначает прямую адресацию. Комбинация

MOD =01 означает, что третий байт команды содержит 8-битное смещение, которое

до вычисления эффективного адреса автоматически расширяется со знаком до 16

бит. Если MOD = 10, третий и четвертый байты команды содержат 16-битное

смещение. Наконец, в случае MOD = 11 операндом является регистр, адрес которого

определяется полем R/M.

Рис. 7.18. Режимы адресации и

сегментные регистры по умолчанию для различных комбинаций полей MOD и R/M

Рис. 7.19. Форматы команды сложения

ADD в следующих операциях: а — прибавить регистр к регистру или памяти и

запомнить результат в регистре или памяти; б — прибавить непосредственный

операнд к регистру (памяти) и поместить результат в регистр (память) ; в —

прибавить непосредственный операнд к АХ (AL) и запомнить результат в АХ (AL) —

специальный случай для аккумулятора

На

Рис. 7.18 также показаны сегментные регистры, используемые в каждой из

комбинаций полей MOD и R/M. Эффективный адрес операнда в памяти определяется

полями MOD и R/M, но 20-битный физический адрес равен сумме эффективного адреса

и содержимого сегментного регистра, умноженного на 16. В режимах адресации с

привлечением регистра ВР с эффективным адресом суммируется содержимое

сегментного регистра SS, а в остальных режимах адресации участвует регистр DS.

Чтобы

изменить используемые в соответствии с Рис. 7.18 сегментные регистры,

предусмотрена специальная однобайтная команда, называемая префиксом замены

сегмента. Она имеет следующий формат:

![]()

Если

команде предшествует префикс замены сегмента, при обращении к данным в процессе

ее выполнения участвует сегментный регистр REG. Для приведенных на Рис. 7.18

режимов адресации регистр DS можно заменить на CS, SS или ES, а регистр SS при

участии в адресации регистра ВР — на DS, CS или ES. Замену нельзя производить в

следующих специальных случаях:

при

вычислении адреса следующей выполняемой команды в качестве сегментного регистра

всегда применяется CS;

при

участии в адресации регистра SP сегментным регистром всегда служит SS (о

стековых операциях см. гл. 4);

в цепочечных

командах в качестве сегментного регистра Операнда-получателя всегда

используется ES (подробнее см. гл. 5).

Чтобы

глубже разобраться в машинных командах микропроцессора 8086, рассмотрим команду

сложения ADD. В команде ADD содержимое операнда-источника прибавляется к

содержимому операнда-получателя и сумма заменяет содержимое

операнда-получателя. В зависимости от режима адресации команда ADD принимает

одну из трех форм, представленных на Рис. 7.19.

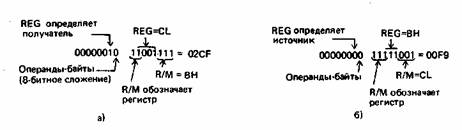

На

Рис. 7.20 показан машинный код двух команд ADD, каждая из которых выполняет

следующую операцию:

(CL)«-(BH)

+ (CL).

В

первой команде бит D = 1 указывает, что сумма помещается в регистр REG = 001 =

CL. Комбинация MOD =11, поэтому R/M обозначает регистр 111= ВН. Во второй

команде бит D = 0, поэтому регистр REG =111 = ВН служит источником. По-прежнему

MOD = 11 и R/M обозначает регистр, которым здесь является 001 = CL.

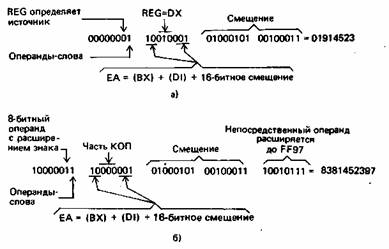

На

Рис. 7.21, а показана команда, в которой для сложения содержимого ячейки памяти

и регистра применяется относительный базовый индексный

Рис. 7.20. Две эквивалентные команды

прибавления содержимого регистра ВН к содержимому CL: когда REG определяет

получатель (а) и когда REG определяет источник (б)

Рис. 7.21. Два примера команды ADD с

относительным базовым режимом адресации: а — сложение регистра с памятью, б —

сложение непосредственного операнда с памятью

режим

адресации. Состояние D = 0 показывает, что сумма помещается в ячейку памяти, а

бит W = 1 означает 16-битное сложение. Эффективный адрес равен сумме (ВХ), (DI)

и 16-битного смещения, которое равно 2345. Если (ВХ) = 0892 и (DI) = 59A3, то

ЕА

= 0892 + 59АЗ + 2345 = 857А.

На

Рис. 7.21,б показана похожая команда, которая прибавляет к содержимому ячейки

памяти непосредственный операнд.

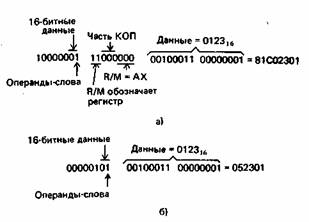

Некоторые команды имеют длинную и короткую формы. Эти

формы команды, которая прибавляет непосредственный операнд к регистру АХ,

показаны на Рис. 7.22. Так как S:W = 01, команда содержит два байта данных. В

длинной форме регистр АХ явно указан полем R/M, а в короткой форме АХ неявно

определяется кодом операции.

Рис. 7.22. Длинная (а) и короткая (б)

формы прибавления непосредственного операнда к регистру АХ

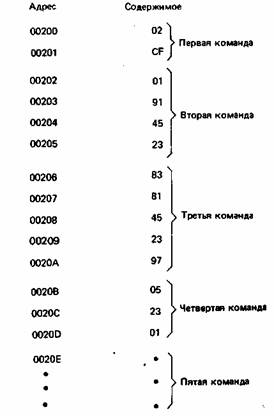

Рис. 7.23. Последовательность команд

в памяти

На

Рис. 7.23 показано размещение команд из Рис. 7.20, а, 2.18 и 2.19,6 в памяти,

начиная с адреса 00200. Если содержимое CS равно 0018, при выполнении этих

команд будет произведен инкремент IP от 0080 до 008Е.