80186

Микросхема

80186 представляет собой усовершенствованный вариант процессора 8086 с

внутренними генератором синхронизации, логикой управления прерываниями, схемой

таймеров, контроллерами ПДП и программируемыми схемами выбора кристалла.

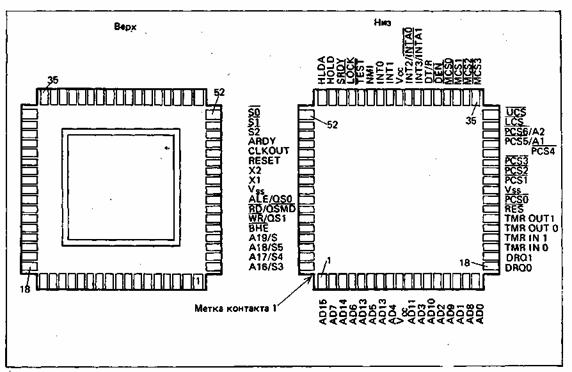

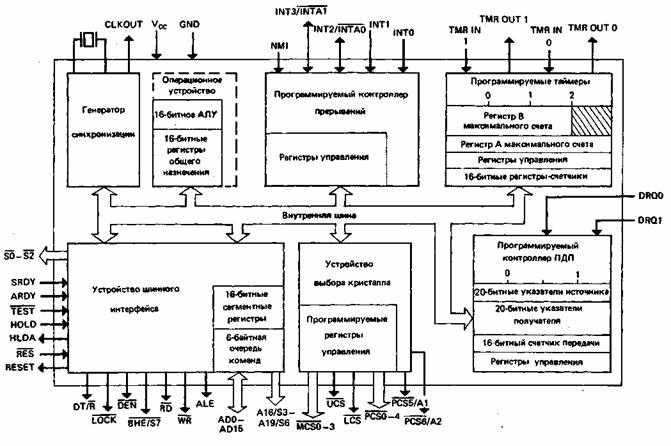

Разводка контактов и схема процессора 80186 приведены на Рис. 1., откуда видно,

что он имеет 68 контактов и размещен в корпусе с 4-сторонним расположением

контактов (выводов).

Сигналы

на линиях ![]() , NMI, A19/S6-A16/S3, AD15-AD0,

, NMI, A19/S6-A16/S3, AD15-AD0, ![]() /S7, LOCK и S2-S0 имеют такие же смысл и временные диаграммы,

что и у микропроцессора 8086 в максимальном режиме. Благодаря такой

совместимости в системах с процессором 80186 можно применять микросхемы

управления шиной 8288 и 8289, а также внешние процессоры 8087 и 8089, которые

разработаны для семейства 8086/8088. Сигналы DT/

/S7, LOCK и S2-S0 имеют такие же смысл и временные диаграммы,

что и у микропроцессора 8086 в максимальном режиме. Благодаря такой

совместимости в системах с процессором 80186 можно применять микросхемы

управления шиной 8288 и 8289, а также внешние процессоры 8087 и 8089, которые

разработаны для семейства 8086/8088. Сигналы DT/![]() ,

, ![]() , HOLD и HLDA выполняют такие же функции, что и у

микропроцессора 8086 в минимальном режиме. Назначения сигналов ALE/QS0,

, HOLD и HLDA выполняют такие же функции, что и у

микропроцессора 8086 в минимальном режиме. Назначения сигналов ALE/QS0, ![]() /QS1 и

/QS1 и ![]() /

/![]() определяются в

процессе сброса по результату опроса сигнала

определяются в

процессе сброса по результату опроса сигнала ![]() /

/![]() Если он имеет низкий

уровень (т. е. подключен на землю), процессор 80186 переводится в режим

состояния очереди и сигналы ALE/QSO и

Если он имеет низкий

уровень (т. е. подключен на землю), процессор 80186 переводится в режим

состояния очереди и сигналы ALE/QSO и ![]() /QS1 отражают состояние очереди (как в максимальном режиме

микропроцессора 8086), а сигнал

/QS1 отражают состояние очереди (как в максимальном режиме

микропроцессора 8086), а сигнал ![]() /

/![]() при обычной работе не

играет роли; в противном случае (RD/QSMD = 1) сигналы ALE,

при обычной работе не

играет роли; в противном случае (RD/QSMD = 1) сигналы ALE, ![]() и

и ![]() действуют как в

минимальном режиме микропроцессора 8086. Вход синхронной готовности SRDY

аналогичен входу READY микропроцессора 8086 и должен синхронизироваться извне.

Процессор 80186 имеет одно напряжение питания +5 В, которое подается на вход

Vcc. Контакты Vss предназначены для системной земли. Все остальные сигналы

процессора 80186 в микропроцессоре 8086 отсутствуют.

действуют как в

минимальном режиме микропроцессора 8086. Вход синхронной готовности SRDY

аналогичен входу READY микропроцессора 8086 и должен синхронизироваться извне.

Процессор 80186 имеет одно напряжение питания +5 В, которое подается на вход

Vcc. Контакты Vss предназначены для системной земли. Все остальные сигналы

процессора 80186 в микропроцессоре 8086 отсутствуют.

Линии

ARDY, ![]() , RESET, CLKOUT, X1 и Х2 подключены к внутреннему генератору

синхронизации, похожему на генератор 8284А. Сигнал на входе асинхронной

готовности ARDY аналогичен входу RDY генератора 8284А и синхронизируется

внутренней схемой генератора синхронизации. Вход

, RESET, CLKOUT, X1 и Х2 подключены к внутреннему генератору

синхронизации, похожему на генератор 8284А. Сигнал на входе асинхронной

готовности ARDY аналогичен входу RDY генератора 8284А и синхронизируется

внутренней схемой генератора синхронизации. Вход ![]() предназначен для

подачи сигнала сброса, а сигнал RESET представляет собой синхронизированный

выход сигнала

предназначен для

подачи сигнала сброса, а сигнал RESET представляет собой синхронизированный

выход сигнала ![]() . Выходной сигнал синхронизации CLKOUT требуется в логике

управления шиной и интерфейсах. Осциллятор (кварц), определяющий частоту

синхронизации (она установлена равной 8 МГц), подключается на входы X1 и Х2.

. Выходной сигнал синхронизации CLKOUT требуется в логике

управления шиной и интерфейсах. Осциллятор (кварц), определяющий частоту

синхронизации (она установлена равной 8 МГц), подключается на входы X1 и Х2.

Линии

INTO, INT1, INT2/![]() и INT3/

и INT3/![]() подключаются к логике управления прерываниями. Использование

их зависит от режима, который определяется битами в регистрах управления,

находящихся в контроллере прерываний. В режиме iRMX 86 контроллер 8259А должен

применяться как основное устройство управления прерываниями и необходима

специальная -программа инициализации. Режим iRMX 86 делает контроллер

совместимым с операционной системой iRMX 86, а три других режима не относятся к

iRMX 86. Это режимы:

подключаются к логике управления прерываниями. Использование

их зависит от режима, который определяется битами в регистрах управления,

находящихся в контроллере прерываний. В режиме iRMX 86 контроллер 8259А должен

применяться как основное устройство управления прерываниями и необходима

специальная -программа инициализации. Режим iRMX 86 делает контроллер

совместимым с операционной системой iRMX 86, а три других режима не относятся к

iRMX 86. Это режимы:

Вложенный. Все четыре линии применяются как входы запросов

прерываний, а внутренняя работа контроллера примерно напоминает работу микросхемы

8259А, но имеются четыре входа запросов прерываний вместо восьми и не

разрешается подключать ведомые контроллеры 8259А.

Рис. 1.. Разводка контактов корпуса и

схема процессора 80186

Рис. 1.. Разводка контактов корпуса и

схема процессора 80186 (окончание)

Каскадный. Пары INT0-INT2/![]() и INT1-NT3/

и INT1-NT3/![]() действуют как пары

запрос/подтверждение. Каждую из них можно подключить к отдельному устройству,

приоритетной цепочке, контроллеру 8259А или каскадно включенным 8259А. В

последнем варианте каждая пара может обслуживать до 64 линий прерываний.

действуют как пары

запрос/подтверждение. Каждую из них можно подключить к отдельному устройству,

приоритетной цепочке, контроллеру 8259А или каскадно включенным 8259А. В

последнем варианте каждая пара может обслуживать до 64 линий прерываний.

Специальный

вложенный. Аналогичен предыдущему режиму, но каскадированные ведущие

контроллеры 8259А работают в специальном вложенном режиме.

Процессор

80186 имеет три таймера, один из которых подключен к паре TMR IN 0 и TMR OUT 0,

другой - к паре TMR IN 1 и TMR OUT 1, а третий внешне недоступен, но может быть

делителем первых двух таймеров или источником запросов в одном из внутренних

контроллеров ПДП. Выполняемая таймером функция зависит от режима работы. Внешне

доступные таймеры можно перевести в один из нескольких режимов, в которых входы

TMR IN используются для подачи сигналов управления или синхронизации, а выходы

TMR OUT формируют одиночные импульсы или непрерывные сигналы.

Линии

![]() ,

, ![]() ,

, ![]() -

-![]() ,

,![]() -

-![]() ,

, ![]() /A1 и

/A1 и ![]() /A2 подключены к логике выбора кристалла и позволяют интерфейсам

получать сигналы выбора кристалла непосредственно от процессора 80186. При этом

логика дешифрирования адреса в этих интерфейсах не требуется. Первые шесть из

указанных линий предназначены для выбора модулей, адреса которых находятся в

пространстве памяти, а последние семь формируют сигналы выбора кристаллов для

интерфейсов с адресами в пространстве ввода-вывода.

/A2 подключены к логике выбора кристалла и позволяют интерфейсам

получать сигналы выбора кристалла непосредственно от процессора 80186. При этом

логика дешифрирования адреса в этих интерфейсах не требуется. Первые шесть из

указанных линий предназначены для выбора модулей, адреса которых находятся в

пространстве памяти, а последние семь формируют сигналы выбора кристаллов для

интерфейсов с адресами в пространстве ввода-вывода.

Для

сигналов выбора памяти начальные адреса и размеры модулей, воспринимающих

сигналы, программируются с помощью регистров управления в секции выбора

кристалла. Однако модуль, подключаемый к ![]() должен находиться в

самой верхней части памяти (которая кончается адресом FFFFF), а модуль,

подключаемый к

должен находиться в

самой верхней части памяти (которая кончается адресом FFFFF), а модуль,

подключаемый к ![]() , должен начинаться с адреса 00000. Линия

, должен начинаться с адреса 00000. Линия ![]() обычно применяется для

выбора ПЗУ, содержащего код инициализации, выполняемый после сброса. С сигналом

обычно применяется для

выбора ПЗУ, содержащего код инициализации, выполняемый после сброса. С сигналом

![]() ассоциируется память,

которая содержит указатели прерываний и, возможно, секцию системного кода.

Модуль, подключаемый к любой из этих линий, может иметь размер 2" К байт, n = 0 ... 8. Линии MCS3-MCSO можно использовать для

выбора модулей с размерами 2nК

байт, n = 1 ... 7, но размеры всех модулей должны быть

одинаковыми. Модули должны быть смежными в адресном пространстве с модулем,

соответствующим MCSO и имеющим начальный адрес, который кратен 4 х 2nК, где 2nК - длина модулей.

ассоциируется память,

которая содержит указатели прерываний и, возможно, секцию системного кода.

Модуль, подключаемый к любой из этих линий, может иметь размер 2" К байт, n = 0 ... 8. Линии MCS3-MCSO можно использовать для

выбора модулей с размерами 2nК

байт, n = 1 ... 7, но размеры всех модулей должны быть

одинаковыми. Модули должны быть смежными в адресном пространстве с модулем,

соответствующим MCSO и имеющим начальный адрес, который кратен 4 х 2nК, где 2nК - длина модулей.

Каждая

линия периферийного выбора кристалла ассоциируется со 128-байтным блоком

адресного пространства и все блоки должны быть смежными. Соответствующий ![]() начальный адрес можно

запрограммировать на любой адрес, кратный 128, но после его задания начальный

адрес, соответствующий

начальный адрес можно

запрограммировать на любой адрес, кратный 128, но после его задания начальный

адрес, соответствующий ![]() , равен сумме этого адреса и 128 и т. д. Разумеется, при

задании начальных адресов линий выбора периферийных устройств и памяти

необходимо избегать конфликтных назначений. Двухфункциональные линии

, равен сумме этого адреса и 128 и т. д. Разумеется, при

задании начальных адресов линий выбора периферийных устройств и памяти

необходимо избегать конфликтных назначений. Двухфункциональные линии ![]() /A1 и

/A1 и ![]() /A2 можно использовать для периферийных выборов кристалла либо

как защелки линий адреса А1 и А2. Во второй ситуации они обычно подключаются на

входы А0 и А1 8-битных интерфейсных микросхем.

/A2 можно использовать для периферийных выборов кристалла либо

как защелки линий адреса А1 и А2. Во второй ситуации они обычно подключаются на

входы А0 и А1 8-битных интерфейсных микросхем.

Число

состояний ожидания (0, 1, 2 или 3) допускается программировать для каждой

группы линий выбора. Для этого предназначены 3 младших бита соответствующего

регистра управления.

Процессор

80186 имеет два независимых контроллера ПДП, причем запросы этих контроллеров

осуществляются по входам DRQ0 и DRQ1. Линии явных сигналов подтверждения ПДП

отсутствуют. Подтверждение можно реализовать с помощью сигналов считывания или

записи, а также одной или двух линий выбора кристалла. Каждый контроллер может

пересылать блоки размером до 64К байт или слов. Передача байт или слов

определяется битом в регистре управления контроллера. Еще один бит в этом

регистре определяет, будет прерывание или нет при достижении счетчиком нуля.

Внешний сигнал об этом условии отсутствует.

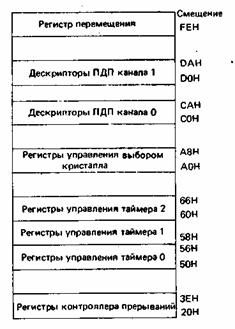

Все

регистры управления находятся в 256-байтном блоке адресного пространства (Рис. 2.).

Базовый адрес этого блока определяется регистром управления, у которого

смещение в блоке равно FE, а обращения ко всем регистрам управления

осуществляются в соответствии с содержимым данного регистра. При сбросе

содержимое этого регистра устанавливается таким, что базовый адрес блока равен

FFOO в пространстве ввода-вывода.

Рис. 2.. Карта регистров управления

Это

обычное размещение блока регистров управления, но его можно переместить во

время инициализации системы, изменяя содержимое регистра со смещением FE (т. е.

базового адреса регистров управления).

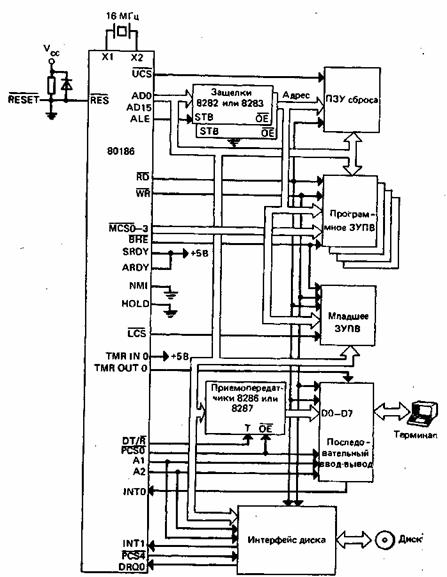

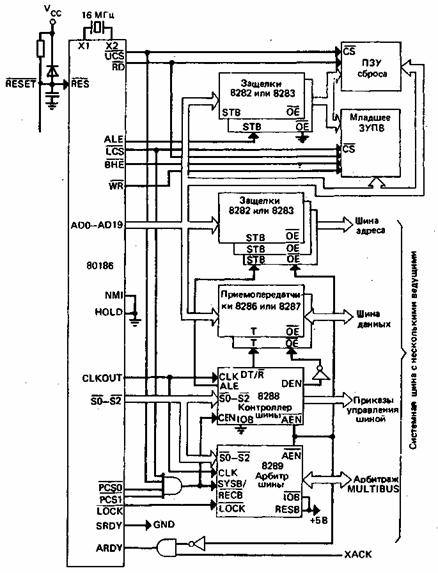

Рис.

3 иллюстрирует типичную конфигурацию малой системы на базе процессора 80186, а

более сложная система, которая может подключаться к шине с несколькими

ведущими, показана на Рис. 4. Отметим в обоих случаях сокращение числа

микросхем (корпусов).

Рис. 3. Небольшая система на базе

процессора 80186

Кроме

наличия внутренних компонент, реализующих разнообразные функции, процессор

80186 имеет вдвое более высокую производительность

Рис. 4. Процессор 80186 в

мультипроцессорной системе с несколькими ведущими

по

сравнению с микропроцессором 8086, а его линии-адреса/данных и некоторых

сигналов управления имеют вдвое большую нагрузочную способность, Наконец, в ней

предусмотрены следующие дополнительные команды:

Непосредственно

включить (в стек) и извлечь (из стека). Для включения и извлечения

непосредственных значений.

Включить

все (PUSHA) и извлечь все (POPА). Для включения и извлечения всех регистров

одной командой.

Знаковое

непосредственное умножение. Для умножения на непосредственный операнд.

Сдвиг/циклический

сдвиг на счетчик. Счетчиком является непосредственный операнд.

Ввод

цепочки (INS) и вывод цепочки (OUTS). Позволяет вводит и выводить цепочки,

пользуясь префиксом повторения REP.

Войти

(ENTER) и выйти (LEAVE) из процедуры. Команда ENTER опредс-деляет, сколько байт

динамической памяти распределить стековому кадру для вызываемой процедуры. Она

также определяет уровень вложения процедуры и задает, сколько указателей ЦП

будут копироваться в новом кадре из предыдущего кадра. Команда LEAVE выполняет

действия, обратные действиям команды ENTER. Данные команды помогают реализовать

языки высокого уровня с блоковой структурой.

Обнаружить значение вне диапазона (BOUND).

Контролирует содержимое заданного в команде регистра в границах, определяемых

адресуемым командой двойным словом. Применяется в основном для задания границ

массивов.