|

|

7.1.11. Математический

сопроцессор 8087

Сопроцессор

8087, официально (фирмой Intel) называемый NPX (Numeric Processor extension), предназначен для расширения вычислительных

возможностей центрального процессора 8086/8088, 80186/80188. Его применение к

системе команд 8086 добавляет 68 мнемоник, включающих арифметические,

тригонометрические, экспоненциальные и логарифмические инструкции. Сопроцессор

поддерживает 7 типов данных: 16-, 32-, 64-битные целые числа; 32-, 64-,

80-битные числа с плавающей точкой и 18-разрядные числа в двоично-десятичном

формате. Формат чисел с плавающей точкой соответствует стандарту IEEE 754.

Сопроцессор выполняет математические операции аппаратно с производительностью,

превосходящей их программную эмуляцию основным процессором более чем в 100 раз.

Иногда его обозначают как FPU (Floating Point Unit — процессор чисел с

плавающей точкой), что не охватывает иные типы данных, или NPU (Numeric Processing Unit — числовой процессор), что не подчеркивает его

принципиальную зависимость от центрального процессора. С программной точки

зрения связка CPU+NPX выглядит как единое целое, где CPU осуществляет общее

управление процессом и отработку команд основного набора, а NPX исполняет

только свои специфические команды.

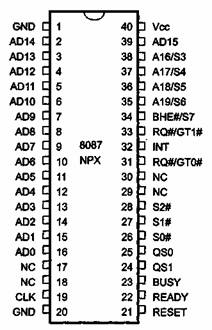

Аппаратный

интерфейс и расположение выводов практически повторяет процессор 8086/8088,

работающий в максимальном режиме (рис. 7.26). Одноименные выводы (кроме RQ/GT1)

сопроцессора и основного процессора соединяются между собой. Для обеспечения

синхронизации вывод BUSY, сигнализирующий о занятости сопроцессора выполнением

инструкции, соединяют со входом TEST

CPU.

Выход INT (Interrupt) используется для сигнализации

(высоким уровнем) о возникновении немаскированного исключения, возникающего во

время выполнения инструкции. Исключением (exception)

называют особые условия, которые могут возникнуть в результате вычислений. В PC

сигнал INT через логическую схему поступает на вход NMI CPU и вызывает

немаскируемое прерывание (вектор 2).

Рис. 7.26. Расположение выводов

сопроцессора 8087

Сопроцессор,

отслеживая сигналы состояния CPU (S[0:2] и QSO, QS1), вместе с ним

просматривает и декодирует инструкции. Сопроцессор имеет внутреннюю очередь

инструкций, работающую по той же логике, что и очередь CPU. ХРХ 8087 может

работать как с 8086, так и с 8088, имеющими различные

параметры очереди и разрядность передаваемых данных. Настроиться на конкретный

тип CPU позволяет проверка состояния сигнала BHE#/S7 непосредственно после

аппаратного сброса (сигнала RESET). Любая команда, предназначенная для

сопроцессора, является двухбайтной инструкцией ESCAPE (первый байт имеет

двоичный код ИОИххх, второй байт вместе с битами ххх уточняет команду), за которой может следовать 1 или 2

байта смещения. Эти команды CPU и NPX отрабатывают одновременно. Если команда

подразумевает обмен данными с памятью, CPU вычисляет их адрес и выполняет

шинный цикл фиктивного чтения первого слова (для 8088 — байта), но игнорирует

считанные данные. Если должно выполняться считывание из памяти, эти данные

реально считываются сопроцессором, который фиксирует во внутреннем регистре и

значение текущего адреса. Если команда подразумевает считывание более, чем одного слова (байта) данных, сопроцессор по линии

RQ/GTO запрашивает управление локальной шиной и, получив его, продолжает

загрузку оставшейся части операнда, последовательно увеличивая адрес. Если

требуется запись в память, то сопроцессор во время фиктивного чтения только

перехватывает значение физического адреса памяти, а реальную запись производит начиная с этого адреса, получив управление шиной.

Таким образом, сопроцессор разгружается не только от разборки «чужих» команд,

но и от всех хитростей формирования физического адреса, принятых в 8086. После

отработки всех циклов передачи (часть из которых может выполняться

сопроцессором во время захвата шины) процессор переходит к выполнению следующей

инструкции. После вычислительной инструкции, исполняемой сопроцессором, должна

следовать команда WAIT (или FWAIT, что одно и то же), по которой процессор дожидается

низкого уровня сигнала на входе TEST# (CPU) — выходе BUSY (NPX). Сигнал

занятости BUSY вырабатывается сопроцессором на время выполнения вычисления, чем

и обеспечивается его синхронизация. Команду WAIT целесообразно вводить не сразу

после команды вычисления, а непосредственно перед тем, как потребуются

результаты вычислений — тогда процессор и сопроцессор могут некоторое время

работать параллельно.

|

|