7.4.4.3.3. Кэш-память в МП 80386

Кэш-памятью прототипа является кэш-память прямого

отображения объемом 64

Кбайт с 16384 входами. Каждый вход содержит 32 бит данных вместе с 16 бит теговой информации. Длина строки

(единица передачи данных между кэш-памятью и ДОЗУ) составляет 32 бит. Десять микросхем памяти

включают восемь статических ОЗУ данных с организацией 8К х 8 и два ДОЗУ

тегового поля с организацией 8К х 8. Для управления кэш-памятью используются

два компаратора и две программируемые логические матрицы. Интерфейс и буферы выполнены на восьми

дополнительных

логических микросхемах. Биты присутствия не обязательны, так как всегда предполагается, что

каждый вход содержит 32-разрядное двойное слово достоверной информации. Подсистема кэш-памяти

использует буферизованную сквозную запись для обновления ДОЗУ. Для МП 80386 комбинация

кэш-память-ДОЗУ

обеспечивает отсутствие тактов ожидания при записи. Процессор использует около четырех тактов ожидания во

время кэш-промахов при чтении.

В кэш-памяти прямого отображения каждый элемент в ДОЗУ

отображается в один

элемент внутри кэш-памяти. Отображение осуществляется путем разделения 30-разрядного

физического адреса процессора на две части: 16-разрядный тег и 14-разрядный индекс. Тег

соответствует старшему адресу строк (А16-А31), а индекс - младшему адресу строк (А2-А15). Так как

каждый элемент ДОЗУ с

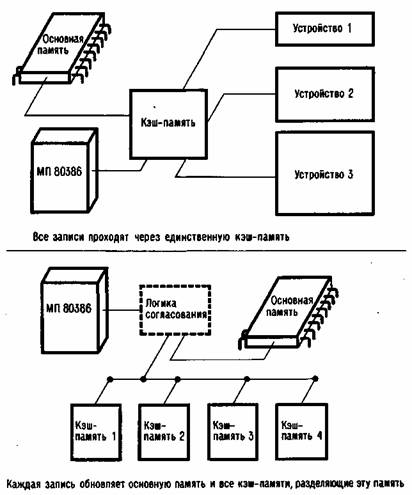

Рис. 4.10. Использование

аппаратуры кэш-памяти.

одинаковыми значениями А2-А15 отображается в

соответствующее место в кэш памяти, то лишь один из этих элементов может быть

представлен в кэш-памяти в любой момент

времени.

Поля тега и индекса совместно определяют место двойного

слова в основной памяти.

В дополнение к этому индекс выбирает одно из 16384 мест в кэш-памяти. Самые младшие два бита адреса

кодируются так, что становятся доступными все четыре байта слова, бит А31 определяет различия

между некэшируемыми адресами ЭППЗУ и кэшируемыми адресами ДОЗУ. Если требуемые данные находятся в кэш-памяти, то чтение может быть

выполнено за цикл в 2 такта. В противном случае чтение требует шести тактов. Ключ к успеху в

конструировании системы с кэш-памятью лежит в увеличении числа двухтактовых циклов магистрали

относительно шеститактовых. Это достигается увеличением объема кэш-памяти с 16

до 64 Кбайт.

Кэш-память

использует буферизованную сквозную запись для обновления ДОЗУ. Во время циклов записи новые данные

записываются в кэш-память и одновременно

в ДОЗУ. При использовании буфера цикл записи в ДОЗУ перекрывается по времени со следующим циклом магистрали.

Это перекрытие позволяет выполнить

запись только за три такта.

Буферизованная сквозная запись реализована путем

отделения режима работы машины с кэш-памятью от режима работы с ДОЗУ. Поскольку как кэш-память,

так и ДОЗУ имеют

свои собственные контроллеры, то операция с перекрытием этих функций возможна.

В режиме работы с кэш-памятью программируемая логическая матрица определяет, когда

необходим цикл обращения к памяти, тогда как в режиме работы с ДОЗУ этот запрос проверяется только

в случае готовности к запуску нового цикла.