7.4.4.2.1. Интерфейс с основной

памятью

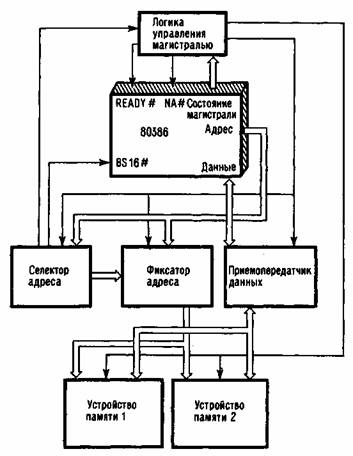

Рис. 4.4. Структурная схема основного

интерфейса с памятью.

Построение системы памяти из отдельных блоков можно

представить как заполнение пространства памяти. Это пространство можно

рассматривать как прямоугольную область, которая разделена на ряды,

соответствующие возможным адресным комбинациям. Каждый ряд состоит из нескольких битов,

образующих слово данных.

После размещения блоков памяти в пространстве остается определить необходимые

взаимосвязи между ними. Каждая из линий данных блока памяти подключается к соответствующей

линии шины данных процессора. Линии адреса используются сначала для выбора

блока памяти или параллельной группы блоков, а затем для определения слова внутри выбранного

блока или блоков. Структурная схема на рис. 4.4 показывает, какие сигналы управления формирует логика

управления

магистралью для буферов данных, фиксаторов адреса памяти и устройств памяти. Она также формирует

активный сигнал READY # для завершения цикла магистрали МП 80386 и сигнал NA# для

управления конвейеризацией адреса. На основе адресных выходов МП 80386 селектор адреса

генерирует сигналы выбора микросхем памяти и сигналы BS16#.