7.4.4.1.3. Разбиение на страницы и

их трансляция

Разбиение на страницы - это другой способ управления

памятью, удобный для многозадачных операционных систем. Разбиение на страницы

возможно только в защищенном

режиме и обеспечивает управление очень большими сегментами МП 80386. С помощью этого

способа программы разделяются на одинаковые по размеру страницы в отличие от

сегментации, которая представляет программы и данные в виде сегментов

переменной длины. Фактически разбиение на страницы - это способ более низкого уровня,

чем сегментация. Это означает, что механизм разбиения на страницы транслирует защищенный

линейный адрес, который поступает от блока сегментации в физический адрес. Механизм разбиения на

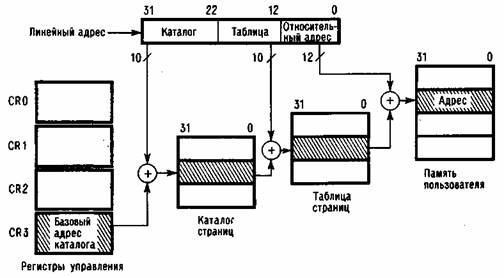

страницы МП 80386 иллюстрируется рис.

4.1.

Во второй фазе трансляции адреса МП 80386 преобразует

линейный адрес в физический адрес, определяя таблицу страниц, страницу внутри

этой таблицы и относительный

адрес внутри данной страницы. Этап трансляции страниц не является обязательным. Трансляция страниц возможна,

только когда установлен бит PG регистра

CRO. Этот бит обычно устанавливается операционной системой во время программной инициализации.

Он должен быть установлен, если операционная

система предполагает использовать множественные задачи виртуального МП

Рис. 4.1. Механизм разбиения памяти на

страницы.

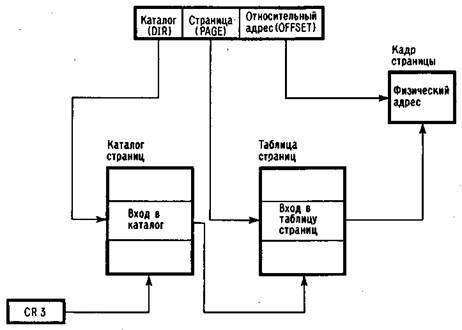

Рис. 4.2. Трансляция страницы.

8086, странично - ориентированную виртуальную память или

странично - ориентированную

защиту.

Линейный адрес состоит из трех полей: DIR

(каталог), PAGE (страница)

и OFFSET (относительный

адрес). На рис.

4.2 показано, как МП 80386 преобразует линейный адрес в физический. Механизм

адресации использует поле DIR в качестве индекса в каталоге страниц, а поле OFFSET для

указания байта внутри страницы, определяемой таблицей страниц.

Кадр страницы - это блок в 4 Кбайт физической памяти.

Страницы начинаются на

границах 4-Кбайт областей памяти и фиксированы по размеру. Страницы не имеют непосредственного

отношения к логической структуре программы. Адрес кадра страницы* указывает физический начальный адрес

страницы и его младшие 12 битов всегда равны

нулю. В каталоге страниц адрес кадра страницы - это адрес таблицы страниц. В таблице второго уровня адрес

кадра страницы является адресом кадра

той страницы, которая содержит нужный операнд в памяти.

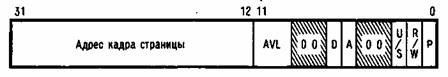

Таблицы

страниц. Это массив 32-разрядных

спецификаторов страниц. Таблица также является

страницей и занимает 4 Кбайт памяти или до 1 К 32-разрядных входов. Формат обращения к таблице страниц (входа)

показан на рис. 4.3.

Этот формат имеет следующие поля:

Бит мусора D(6) и бит доступа А(5). Эти биты содержат информацию об

использовании страницы и устанавливаются аппаратно. Процессор устанавливает

биты доступа в таблицах страниц обоих уровней перед операцией чтения из или записи в страницу. Затем

процессор устанавливает бит мусора в таблице страниц второго уровня перед

операцией записи по адресу, соответствующему входу в эту таблицу. Бит мусора входов

каталога страниц является неопределенным.

В операционной системе, которая поддерживает страничную

виртуальную память,

эти биты используются для определения тех страниц, которые могут быть удалены из физической памяти в

случае, когда требуется больший объем, чем размер доступной в данный момент физической памяти.

Ответственность за проверку

и очистку этих двух битов лежит на операционной системе.

Бит пользователя/супервизора U/S (2) и бит чтения/записи R/W (1). Используются для защиты на уровне

страниц, которую МП 80386 выполняет в то же самое время, что и трансляцию адреса.

Бит присутствия Р, бит 0. Этот бит показывает, может ли

вход в таблицу страниц

использоваться при трансляции адреса. Если может, то Р = 1. Если же Р = О в

таблице страниц любого уровня, то этот вход нельзя использовать для трансляции адреса и остальные поля входа

доступны для использования программой.

Если Р = 0 в таблице страниц любого уровня и сделана

попытка использовать вход

в таблицы страниц для трансляции адреса, то МП 80386 вызывает исключение по

странице.

Рис. 4.3. Формат входа в

таблицу страниц.

Трансляция страниц и комбинации сегментов. Если МП 80386 используется для выполнения программ,

спроектированных для специальных архитектур, не имеющих сегментов, то может

оказаться целесообразным выключить сегментацию. Процессор не имеет специального режима для

подавления сегментации. Однако тот же самый эффект достигается путем начальной загрузки

регистров сегментов

селекторами дескрипторов, которые покрывают полное

32-разрядное пространство линейных адресов. После загрузки таких дескрипторов

регистры сегментов не изменяются. Относительные 32-разрядные адреса команд МП

80386 адресуют все линейное

адресное пространство.

Сегменты могут быть больше или меньше, чем страница

размером в 4 Кбайт. Если

требуемая структура данных больше, чем страница, и операционная система поддерживает страничную

виртуальную память, то операционная система разделяет эту структуру на страницы, любое

количество которых может присутствовать в любой данный момент времени. Это прозрачно для

прикладного программиста. Если требуемая информация меньше, чем страница, то операционная система

может быть

спроектирована так, чтобы комбинировать несколько структур данных внутри одной страницы.

Архитектура МП 80386 допускает несоблюдение прямого

соответствия между границами

страниц и сегментов. Таким образом, сегмент может содержать конец одной

страницы и начало другой. Аналогично страница может содержать конец одного сегмента и начало другого.

Программы управления памятью, однако, можно сделать проще, если использовать некоторую

взаимосвязь между границами страниц и сегментов. Например, логика для резервирования страниц и

сегментов может быть

комбинированной, если сегменты резервируются только целыми страницами. В этом случае логика

для учета частично используемых страниц не нужна.