7.4.1.4.8. Буфер ассоциативной

трансляции

Буфер ассоциативной трансляции (ТЬВ)-это кэш-память,

используемая для трансляции

линейных адресов в физические.

Предупреждение: механизм проверки TLB является уникальным для МП

80386 и может быть

не реализован в том же виде в будущих процессорах. Программы, которые

используют этот механизм в его нынешнем виде, могут оказаться несовместимыми с будущими

процессорами.

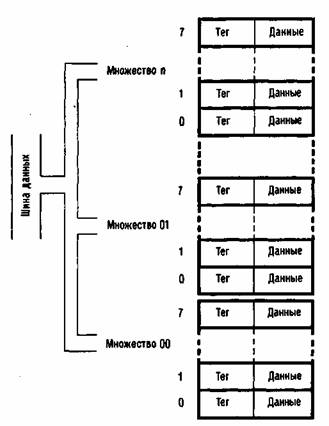

Буфер TLB является четырехканальной

ассоциативной по множеству памятью. Множество-это набор элементов, имеющих некоторое общее

свойство или находящихся

в определенном отношении друг с другом. Структура TLB показана на рис. 1.10. В буфере TLB имеются следующие элементы:

Ассоциативное запоминающее устройство (АЗУ). Адресуемое по

содержимому ячейки

АЗУ содержит 32 линейных адреса и связанные с ними так называемые теговые биты, которые используются для

защиты данных и реализации кэш-памяти.

Запоминающее устройство с произвольной выборкой (ЗУПВ). Адресуемое по номеру

(адресу) ячейки ЗУПВ содержит старшие 20 бит 32-разрядных физических адресов, которые соответствуют

линейным адресам в АЗУ.

Рис. 1.10. Структура буфера

трансляции адресов.

Аппаратная логика реализует четырехканальную кэш-память

и включает двухразрядный

указатель замены, определяющий для каждого из четырех каналов, к какому входу он присоединяется при записи в буфер TLB.

Адреса и команды записываются в буфер TLB через

регистр команд, тогда как данные считываются из или записываются в буфер через

регистр данных. Регистр проверки TR6 является регистром команд при доступе к буферу TLB, а

регистр проверки TR7 используется как регистр данных.

Регистры проверки. Два регистра проверки используются для управления проверкой АЗУ или ЗУПВ в буфере

TLB, а кэш-память-для хранения информации из таблиц страниц. Регистр TR6

является командным регистром проверки, а регистр TR7-регистром данных, который

содержит данные для проверки буфера TLB. (Регистры TRO-TR5 не существуют.)

Эти

регистры доступны в различных вариантах команды MOV, которые определены

как для режима реальных адресов, так и для защищенного режима. В защищенном режиме команда MOV, которая

обращается к этим регистрам, может исполняться только на уровне привилегий 0. Любая попытка

считать из или записать

в любой из этих регистров на любом другом уровне привилегий вызовет обработку исключения общей

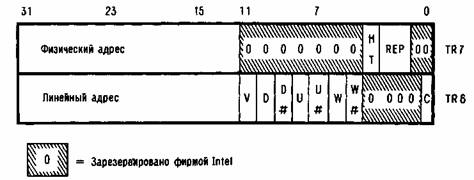

защиты. Формат регистров проверки показан на рис. 1.11.

Регистр

TR6 имеет следующие поля:

Рис. 1.11. Форматы тестовых

регистров.

Линейный адрес-биты 12-31. При записи в буфер TLB для

данного линейного адреса резервируется вход в буфер TLB. Остальные поля входа в буфер TLB

устанавливаются в

зависимости от значения регистра TR7 и значения, только что записанного в регистр TR6. При

просмотре буфера TLB в нем ищется это значение. Если найден один и только один вход в буфер TLB, то остальные поля регистров TR6 и TR7

устанавливаются по найденному входу.

Бит достоверности V-бит 1L Буфер

TLB использует этот бит для определения входов, содержащих достоверные

данные. Достоверность означает, что была проведена успешная трансляция адресов. Входы в буфер TLB, которым не были присвоены определенные

значения, имеют в этом бите нуль. Все биты достоверности могут быть очищены при

записи в регистр управления CR3.

Биты мусора D, D #

-биты 10 и 9. Бит

10 является битом мусора, показывающим, был ли изменен вход в буфер TLB, а бит

9 является его инверсией для/из входа в

буфер TLB.

Биты доступности пользователю U, U # -

биты 8 и 7. Бит

8 является битом доступности

пользователю или системе, а бит 7 является его инверсией для/из входа в буфер TLB.

Биты чтения/записи W, Wtf-биты

б и 5. Бит 6

управляет доступом по чтению/записи, а бит 5 является его инверсией для/из входа в буфер TLB.

Бит команды С-бит 0. В регистре TR6 имеется теговый бит команды и

адреса. Для немедленного просмотра

буфера TLB в регистр TR6

пересылается двойное слово, содержащее в этом бите 1. Для немедленной записи в

буфер TLB в этот регистр

пересылается двойное слово, содержащее в этом бите 0.

Регистр

TR7 имеет следующие поля:

Физический адрес-биты 31-12. Эти биты являются полем данных

буфера TLB. При

записи в TLB вход в этот буфер, зарезервированный для линейного адреса в регистре TR6,

устанавливается по значению этих битов. Если при просмотре буфера TLB

обнаруживается, что бит НТ установлен, то поле данных (физический адрес) считывается в это поле, в

противном случае значение этого поля не определено.

Бит успеха просмотра НТ -бит 4. Для записи в буфер TLB бит НТ

должен быть

установлен. Если просмотр буфера TLB был успешным-НТ = 1, если нет-НТ = 0.

Биты блока с тегом REP-биты З и 2. При записи в буфер TLB должен

быть записан один

из четырех ассоциативных блоков. Эти биты показывают, какой именно. Если при чтении буфера TLB

обнаруживается, что бит НТ установлен, то эти биты показывают, в каком из четырех ассоциативных

блоков был найден тег, иначе их значение не определено.