7.4.1.2.1. Основные блоки

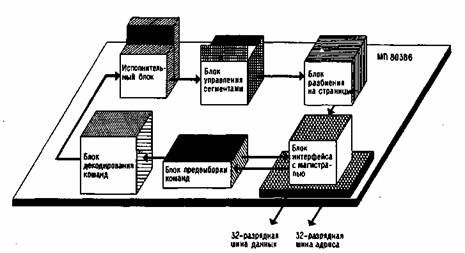

В своей основе МП 80386 состоит из шести блоков,

работающих параллельно: блок интерфейса с магистралью (BIU), блок предварительной выборки

команд, блок декодирования

команд, исполнительный блок (EU), блок управления сегментами и блок разбиения на страницы (рис.

1.3).

Интерфейс представляет собой физическое или логическое

средство, которое соединяет

смежные компоненты, схемы, оборудование или системные элементы. Блок ВШ обеспечивает интерфейс

между МП 80386 и его окружением. Он принимает внутренние запросы для выборки команд от блока

предварительной выборки команд и для обмена данными от блока EU и устанавливает приоритет этих запросов. Одновременно он

генерирует или обрабатывает сигналы для исполнения текущего цикла магистрали. К

ним относятся сигналы адреса, данных и управления для обращения к внешней памяти и устройствам

ввода-вывода. Блок ВШ управляет также

интерфейсом с внешними задатчиками магистрали и сопроцессорами.

Для того чтобы заранее получать команды или данные перед

их фактическим использованием,

существует функция опережающего просмотра программы, которую в МП 80386 выполняет блок

предвыборки команд.

Рис. 1.3. Шесть основных

блоков МП 80386.

Когда блок ВШ не занимает цикла магистрали для исполнения команды, блок

предвыборки команд использует его для последовательной выборки из памяти байтов команд. Эти команды хранятся в 16-байтовой очереди

команд в ожидании обработки блоком декодирования команд.

Блок декодирования команд преобразует байты команды из

этой очереди в микрокод. Декодированные команды в ожидании обработки блоком EU хранятся

в очереди команд

глубиной в три команды, работающей по принципу FIFO («первым вошел - первым

вышел»). Непосредственные данные и относительные адреса в коде операции также берутся из очереди команд.

Блок EU выполняет команды из очереди команд и

взаимодействует со всеми другими блоками, требуемыми для завершения выполнения команды. Для ускорения выполнения команд с

обращением к памяти блок EU приступает к их выполнению до завершения выполнения предыдущей

команды. Так как команды с обращением к

памяти встречаются часто, то благодаря такому перекрытию по времени

производительность повышается примерно на девять процентов.

Регистры общего назначения (РОН) встроенного типа

используются для таких операций, как двоичное сложение или вычисление и модификация адресов.

Они все чаще используются вместо специализированных регистров-аккумуляторов.

Блок EU содержит восемь 32-разрядных РОНов, применяемых как для вычисления

адресов, так и для операций с данными. Этот блок содержит также 64-разрядный

регистр, применяемый

для ускорения операций сдвига, циклического сдвига, умножения и деления.

Блок управления сегментами преобразует логические адреса

в линейные по запросу

блока EU. Для ускорения этого преобразования текущие дескрипторы сегментов помещаются во

встроенную кэш-память. Во время трансляции адресов блок управления сегментами

проверяет, нет ли нарушения сегментации. Эти проверки выполняются отдельно от проверок

нарушений статической сегментации, осуществляемых блоком проверки защиты.

Оттранслированный линейный адрес направляется в блок разбиения на страницы.

Если механизм разбиения на страницы включен,

соответствующий блок транслирует

линейные адреса в физические. Если же этот механизм выключен, то это

означает, что физический адрес совпадает с линейным и

трансляция не нужна. Для ускорения трансляции адресов в кэш-память дескрипторов

страниц помещаются каталог недавно использованных страниц, а также информация о

входах в таблицу страниц

в буфере трансляции адресов. Затем блок разбиения на страницы пересылает физические адреса в блок ВШ

для выполнения цикла обращения к памяти или устройствам ввода-вывода.

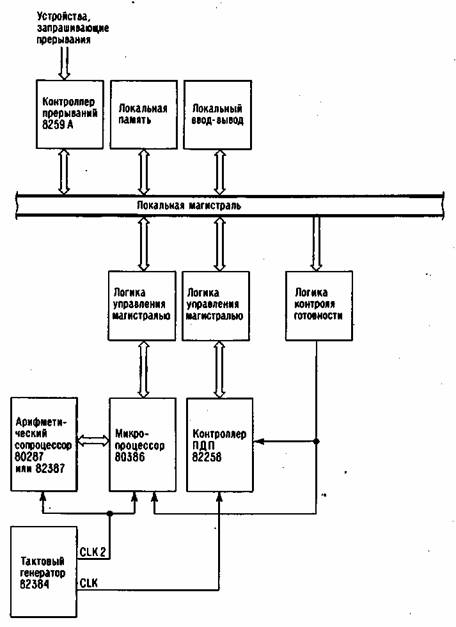

Рис. 1.4. Структурная схема системы на основе

МП 80386.

Микропроцессор 80386 (рис. 1.4) использует 32-разрядные

регистры и шины данных

для поддержки адресов и типов данных такой же разрядности. Благодаря этому

доступ к 32-разрядной памяти может быть завершен всего лишь за два такта генератора, т.е. возможен обмен

информацией по магистрали со скоростью до 32 Мбайт/с при частоте тактового генератора 16 МГц.

Процессор адресует до 4 Гбайт физической памяти и до 64 Тбайт виртуальной памяти.