7.3.9. Два режима работы МП Intel 80286

1.

Обычный.

2.

Защищенный.

1.

В обычном режиме

МП i80286 представляет высокоскоростной процессор i8086 с расширенной системой

команд.

Содержимое сегментного адреса сдвигается влево на 4

бита и складывается со смещением, в результате получается двадцатиразрядный

физический адрес.

Многоуровневый механизм защиты МП гибок: могут

использоваться два, три или четыре уровня защиты для системных программ,

обеспечивая качество защиты, необходимое для конкретной ПЭВМ.

Основной механизм защиты является управляемый доступ

к памяти, при котором каждой задаче предоставляется управляемый доступ к двум

областям виртуальной памяти одной общей и одной частной в соответствии с

содержимым глобальной и локальной дескрипторных таблиц.

2.

В защищенном

режиме содержимое сегментного регистра, называемого селектором, используется

для поиска базового адреса в специальной таблице базовых адресов, находящейся в

ОЗУ. Эта таблица называется дескрипторной или таблицей описания сегментов

памяти, в ней содержатся размеры сегментов и байт с описанием прав доступа к

этим сегментам. Общий размер записи в таблице дескрипторов равен 8 байтам.

Процессор по селектору, хранящемуся в сегментном регистре, находит

соответствующую запись в дескрипторной таблице, считывает значение

24-разрядного базового адреса сегмента, добавляет адрес - смещение и полученный

результат используется как искомый физический адрес байта или слова в ОЗУ. Если

бы процессор всякий раз при генерации физического адреса обращался в ОП за

базовым адресом сегмента, то это привело бы к существенному замедлению его работы.

Поэтому введен в структуру МП i80286 теневой регистр базового адреса сегмента.

При изменении содержимого сегментного регистра процессор из дескрипторной

таблицы, хранимой в ОП, читает в этот теневой регистр информацию о сегменте, в

частности, базовый адрес. Затем для генерации физического адреса используется

не значение базового адреса сегмента из дескрипторной таблицы, а его копия,

хранимая в теневом регистре. То есть в том случае, когда меняем сегмент на

другой, процессор замедляет свою работу по генерации физического адреса.

Следовательно, надо реже заменять сегменты при программировании.

Рабочих дескрипторных таблиц две:

1.

GDT - глобальная

дескрипторная таблица.

2.

LDT - локальная

дескрипторная таблица.

Выбор

таблицы при генерации адреса указывается специальным битом выбора в селекторе

сегмента.

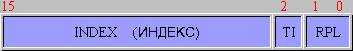

Селектор содержит 3 поля:

· Поле RPL (биты [1,0]) составляют поле уровня

привилегий, используемые для организации системы защиты памяти.

· Поле TI (бит [2]) указывает, какая из двух таблиц

используется для выбора базового адреса сегмента.

o

TI=0

используется GDT

o

TI=1

используется LDT

· Поле [15-3], образованное 13-битами называется полем

индекса (INDEX). Поиск нужной записи в дескрипторной таблице ведется по этому

индексу, который указывает номер восьмибайтной записи с информацией о положении

и длине сегмента.

GDTR - специальный 16-битный регистр определяет

положение и размер глобальной дескрипторной таблицы. Существуют две команды для

Чт и Зп содержимого регистра.

LDTR - специальный 16-битный регистр определяет

местоположение локальной дескрипторной таблицы, в которой хранится селектор для

выбора сегмента с этой таблицей. Информация, на которую ссылается этот

селектор, хранится в GDT - глобальной дескрипторной таблице. Для этого регистра

также имеются специальные команды Чт и Зп.

Таблица векторов прерываний размещается в

произвольном месте ОП, а не обязательно в самом начале, как в МП i8086. Для

этого имеется специальный регистр IDTR по структуре аналогичный регистру GDTR.

Он определяет начало и размер таблицы векторов прерываний. Имеются специальные

команды его чтения и записи.

Регистр IP служит для хранения адреса смещения

следующей исполняемой команды, а регистр F - для хранения флагов.

Регистр MSW - называемый словом состояния или

регистром состояния. Загружая его специальным значением бита РЕ=1, переключаем

режим работы с обычного на защищенный.

· [0] бит РЕ - разрешение защиты.

o

РЕ=0 процессор

работает в реальном режиме.

o

РЕ=1 можно

установить защищенный режим, загрузив MSW, [0]=1.

· [1] МР - бит слежения за процессором. Используется

совместно с битом TS для определения, будет ли команда WAIT генерировать

ловушку особой ситуации 7 (сопроцессор отсутствует). Ловушка генерируется при

установленных МР и TS.

· [2] ЕМ - эмуляция сопроцессора. Установка этого бита

вызывает генерацию ловушки особой ситуации 7 всеми кодами команд сопроцессора.

По умолчанию бит сброшен.

· [3] TS - задача переключена. Автоматически

устанавливается при переключении задач.

· [4] ET - тип сопроцессора

o

ET=0

используется 16-битный протокол 80287

o

ET=1 означает

использование 32-битного протокола 80387

Регистр признаков (F) МП i80286 аналогичен МП i8086,

но имеет дополнительный признак вложенности NT и 2-разрядный признак [13,12]

уровня привилегированности ввода-вывода IOPL, которые позволяют управлять

защищенными операциями ввода-вывода.