7.3.7. Начальный сброс и переход в

защищенный режим

По

высокому уровню сигнала на входе RESET процессор прекращает выполнение

инструкции и перестает управлять локальной шиной. После аппаратного сброса

процессор переходит к выполнению инструкции, считанной по физическому-адресу

FFFFF0h. Сброс (и только сброс!) переводит процессор в реальный режим и

устанавливает значения некоторых регистров:

FLAGS =

0002h, MSW = FFF0h, CS = F000h, IP = FFF0h, DS = ES = SS = 0000h.

После

сброса и до первой команды межсегментного перехода или вызова на шине адреса

биты А[20:23] в циклах выборки команд имеют единичное значение (в реальном

режиме такое возможно лишь в это время). Из этого следует, что по крайней мере

на начальный период времени после сигнала RESET компьютер должен иметь образ

BIOS в адресах FFFFF0-FFFFFFh, в то время как в PC на 8086/88 ROM BIOS

располагалась под границей OFFFFFh. Перемещение BIOS из первого мегабайта

памяти в старшие адреса «навсегда» невозможно, поскольку векторы прерываний,

ссылающиеся на сервисы BIOS, в реальном режиме могут адресоваться только к

памяти в диапазоне адресов 0-0FFFFFh (0-10FFEF при открытом вентиле Gate A20).

Таким образом, у PC/AT на процессоре 80286 (и старше) ROM BIOS отображается по

крайней мере на две области памяти, расположенные под верхними границами

первого и последнего мегабайта физической памяти.

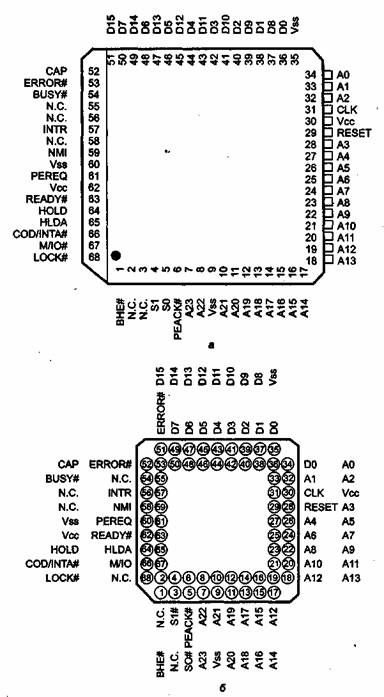

Рис. 2. Расположение выводов

процессора 80286: а — в корпусе PLCC, б — в корпусе РСА

Перевод

процессора в защищенный режим осуществляется загрузкой в MSW слова с единичным

значением бита РЕ (Protect Enable). Перед этим в памяти должны быть

проинициализированы необходимые дескрипторы.

Процессор

80286 имеет механизмы защиты от несанкционированного выполнения критических

инструкций — команды HALT, которая останавливает процессор, и команд, влияющих

на сегменты кода и данных.

Интерфейс

процессора 80286

Процессоры

80286 выпускались в 68-выводных корпусах PLCC и PGA (рис. 2). Их интерфейс

отличается от 8086 применением раздельных шин адреса и данных, конвейерной

адресации, а также составом и назначением управляющих сигналов (табл. 4.4).

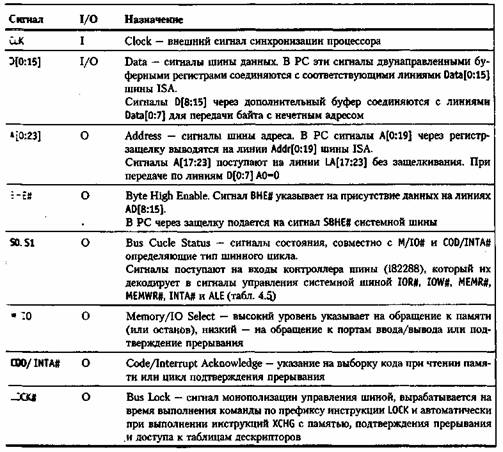

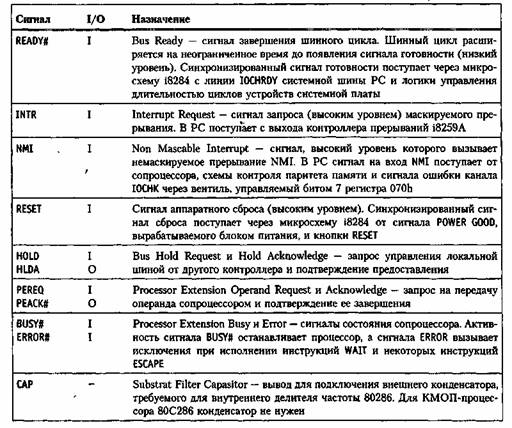

Таблица 1.

Назначение сигналов процессора 80286

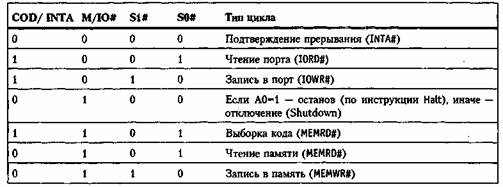

Таблица 2.

Декодирование состояния процессора 80286

Состояния

с S1#=S2#=1 не относятся к циклу идентификации, остальные состояния невозможны.

Шина

адреса позволяет адресовать 16 Мбайт физической памяти в защищенном режиме и 1

Мбайт из области младших адресов — в реальном режиме. Из этого правила для

реального режима есть два исключения:

Линии

А[20:23] после сигнала RESET во время выборки кода находятся в единичном

состоянии до первой инструкции межсегментного перехода.

Линия

А20 может принимать единичное значение, когда сочетание значения сегментного

регистра и эффективного адреса приводят к переходу через границу 0FFFFFh

(максимально возможное значение физического адреса в реальном режиме 10FFEh).

Для обеспечения полной программной совместимости применяют

программно-управляемый вентиль (GATE А20), принудительно обнуляющий бит А20

системной шины адреса.

При

адресации ввода/вывода процессор использует только биты А[0:19] шины адреса

(при этом А[16:19]=0).

Как

и в процессоре 8086, обмен по шине данных возможен байтами или словами. При

побайтном обмене байт с четным адресом (А0=0) передается по линиям D[0:7], с

нечетным (А0=1) — по линиям D[8:15]. Обмен словами с четным адресом происходит

по линиям D[0:15] одновременно. При адресации слова с нечетным адресом

процессор автоматически выполняет два последовательных шинных цикла: первый по

линиям D[8:15], второй — по D[0:7]. Байты шины, участвующие в обмене,

определяются сигналами АО и ВНЕ#.

Синхронизация

процессора осуществляется внешним сигналом CLK, частота которого делится

пополам внутренним делителем для получения сигнала внутренней синхронизации

PCLK (Processor Clock). На внешние выводы процессора сигнал PCLK не поступает,

но его вырабатывает, синхронизируясь сигналами S0# и Sl#, специальная

микросхема 82284 — генератор синхронизации для 80286. Максимальная пропускная

способность локальной шины процессора — одно слово за каждые два цикла

внутренней частоты PCLK.

Конвейерная

адресация (Pipelined Addressing), применяемая в процессоре, предусматривает

возможность начала (фазы идентификации и адресации) нового цикла, не дожидаясь

завершения физического обмена данными предыдущего никла. Это позволяет

сократить количество тактов ожидания, необходимых для согласования с

относительно медленной памятью и портами, за счет более раннего начала выполнения

дешифрации адреса устройством памяти или ввода/выезда. Конвейерный режим

позволяет контроллерами памяти эффективно использовать быстрый страничный режим

динамической памяти и чередование банков.

Процессор

80286 не держит на шине адрес, соответствующий текущему шинному циклу на всем

его протяжении . Для совместимости с шиной -SA, подразумевающей

действительность адреса на все время цикла, сигналы шины адреса процессора

защелкиваются регистрами.

Формирование

управляющих сигналов системной шины IOR#, IOW#, MEMR#, MEMWR#, INTA# и ALE выполняет внешняя микросхема 82288

или ее функциональный аналог из чипсета системной платы.

Управление

временной диаграммой подразумевает задержку (Command delay) z растяжку (Command

extension) командных циклов. Растяжка при необходимости удлиняет командный цикл

обращения для относительно медленных внеш-жнх устройств ввода/вывода и памяти.

Внешние схемы с помощью задержки сигнала READY# могут растягивать цикл на любое

время. При этом вводятся такты ожидания (Wait States) процессора (как и для

8086/88).

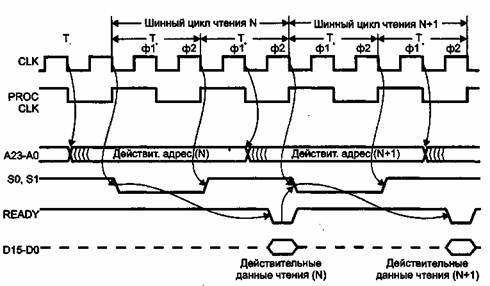

Рис. 4.7. Конвейер шинных циклов

80286

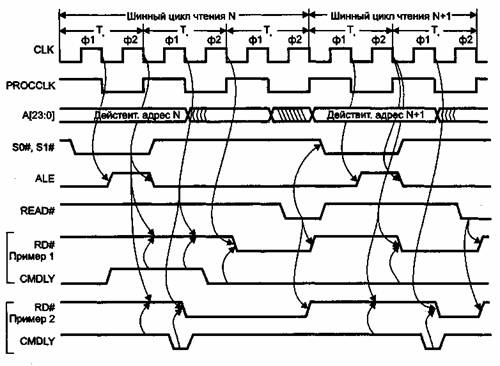

Рис. 3. Задержка и растяжка шинных

циклов 80286

Задержка

предназначена для сдвига начала командного импульса системной шины относительно

соответствующей ему фазы адресации и идентификации (активности ALE). На рис. 3

приведены примеры задержки и растяжки цикла чтения системной шины. Задержка

команд осуществляется микросхемой 82288 (или ее заменителем) по сигналу CMDLY

(Command Delay), который проверяется по каждому спаду CLK.

Необходимость

задержки и растяжки команд появилась в связи с существенным повышением

производительности (относительно 8086) локальной шины процессора.

«Необузданный» 80286 способен генерировать шинные циклы с минимальным периодом

в два такта внутренней частоты (или четыре — внешней). Так, при частоте

процессора 16 МГц шинные циклы пойдут с периодом 250 не (4 МГц). В полной мере

этой производительностью может воспользоваться лишь память и порты

ввода/вывода, подключенные к локальной шине. Устройства на шине ISA такого темпа

не выдерживают. Кроме того, они обычно требуют определенного времени

восстановления (Recovery Time) — пассивного состояния управляющих сигналов шины

между адресованными им командами. Управление задержкой и растяжкой циклов в

зависимости от типа и адреса обращения возлагается на микросхемы чипсета

системной платы, а для задания количества тактов ожидания и времени

восстановления для различных операций в «продвинутых» машинах класса AT ввели

соответствующие опции BIOS SETUP.