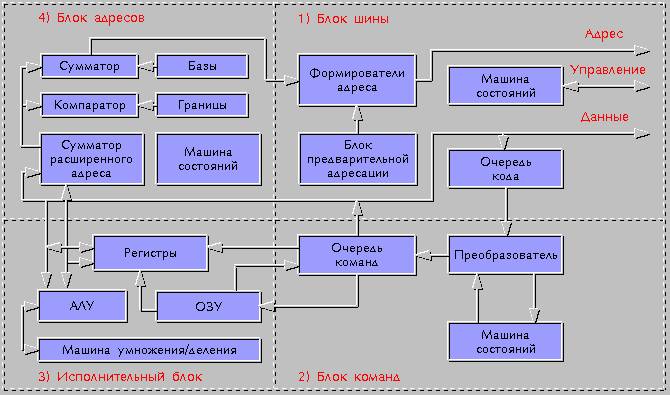

7.3.3. Структура микропроцессора Intel 80286

На рис.1. приведена структура МП Intel 80286.

Рис. 1. Структура микропроцессора i80286.

В МП используется конвейерный принцип выполнения

команд с четырьмя уровнями конвейеризации, реализованными в четырех раздельных

логических блоках:

1.

Шины.

2.

Команд.

3.

Исполнительном.

4.

Адресов.

Эти

блоки работают одновременно; циклы обращения к памяти, вычисления адресов и

контроля защиты, декодирования и выполнения команд могут совмещаться.

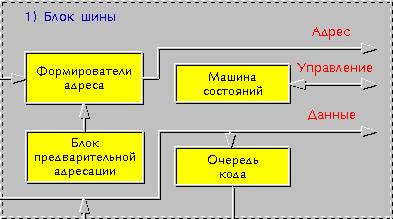

Блок

шины передает информацию из своей очереди в устройство команд со скоростью 1

байт на цикл тактовой частоты.

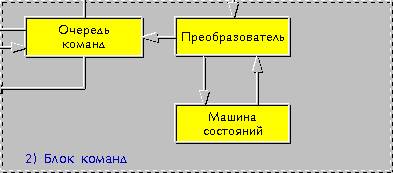

Блок

команд декодирует и преобразует формат полных команд и помещает их в очередь

команд, ожидающих выполнения.

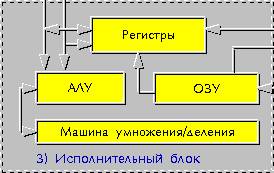

Исполнительный

блок содержит рабочие регистры, АЛУ и микропрограммное ПЗУ, которое определяет

последовательность внутренних микрокоманд. Когда текущая команда завершается,

ПЗУ генерирует сигнал по которому исполнительный блок принимает следующий адрес

ПЗУ из очереди команд. Это обеспечивает постоянную занятость исполнительного

блока.

Устройство

адресов производит преобразование адресов и одновременно контролирует права

доступа. Имеется кэш-память, содержащая базовый адрес, предельное граничное

значение и права доступа для всех сегментов виртуальной памяти для

использования в задаче.

Параллельная работа четырех внутренних устройств дает

возможность МП i80286 осуществлять управление виртуальной памятью и

обеспечивать защиту всей памяти без снижения производительности.