7.5.1.2. Интерфейс процессоров 486

Процессоры

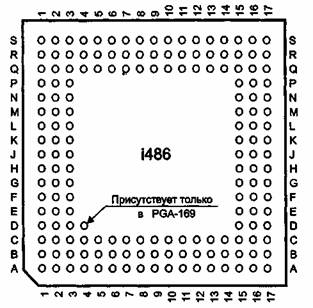

486 исполняются в корпусах PGA-168 или PGA-169 (Рис. 2), PQFP или SQFP. Начиная с

процессоров 486, в системных платах PC стали широко

применяться ZIF-сокеты (Zero Insertion Force

Socket) — «разъемы с нулевым усилием вставки»,

предназначенные для установки процессоров в корпусах PGA со штырьковыми выводами. Унификация расположения

выводов процессоров одного класса и наличие конфигурационных переключателей

позволяет пользователю заменять старые процессоры на более мощные модификации.

Легкость установки требуемого процессора и последующей его замены на более

совершенные модели позволяют выполнять эту операцию даже конечным пользователям.

Для процессоров 486 стали выпускать системные платы, рассчитанные на различные

модификации и тактовые частоты — своеобразный конструктор «собери сам».

Процессоры

487SX выпускались в корпусах PGA-169, имеющих матрицу 17x17. Дополнительный вывод не

нес электрических функций, а использовался как чисто механический ключ для

обеспечения правильной ориентации в гнезде сопроцессора. Вывод В14 (МР — Math Present)

процессора 487SX использовался для сигнализации

присутствия сопроцессора в гнезде. Его постоянный низкий (активный) уровень

сигнала отключал основной процессор (сигналом BOFF#). Системные платы с установленным процессором и

гнездом для сопроцессора широкого распространения (особенно в нашей стране) не

получили, их вытеснили платы с единственным ZIF-сокетом. Вид корпуса PGA-168 и 169 приведен на Рис. 2.

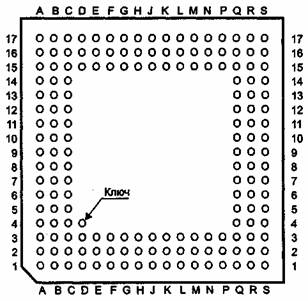

Для

установки процессоров 486 был разработан сокет 1, имеющий 169 контактов матрицы

17x17. Разводка выводов процессоров в корпусах PGA-168 и PGA-169

различается только положением выводов сигналов 1)Р# и FERR#. В универсальных сокетах гнезда А13 и С14 (сигнал FERR#) соединяются вместе, что позволяет в них

устанавливать процессоры с обоими типами корпусов, а гнезда В14 и АИ (сигнал UP#) обычно не используются. Гнездо В14 может

использоваться как сигнал TMS для выбора

режима тестирования по интерфейсу JTAG,

который реализован не во всех моделях 486. Приведенная нумерация контактов

относится к сокету типа 1 с матрицей выводов 17x17.

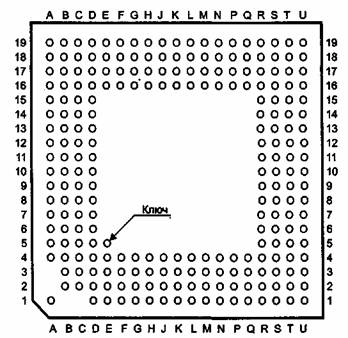

Процессоры

486 могут быть установлены и в сокеты типа 2, 3 или б, имеющих матрицу 19x19,

внешние ряды которой не используется процессорами в корпусах PGA-168 и 169. При этом внутренние три ряда контактов по

назначению совпадают с разводкой выводов процессора 486, но имеют смещенную

нумерацию: ножка А1 корпусов PGA-168 и PGA-169 попадает в гнездо В2 матрицы 19x19. Внешние ряды

матрицы используются как дополнительные контакты питания процессоров Pentium OverDrive.

Сокет

типа 3 отличается от типа 2 возможностью использования питания 3 В.

Малораспространенный сокет 6 имеет питание только 3,3 В. Сигналы,специфичные

для процессоров с WB-кэшем, теоретически могут

присутствовать (или отсутствовать) во всех этих типах сокетов. Вид сокетов

представлен на Рис. 3 и 4.22, их характеристики сведены в табл. 3.2.

Рис. 3. Вид сокета 1

Рис. 2. Процессоры 486 в корпусах PGA-168 и 169

Рис. 4. Вид сокетов 2, 3 и 6

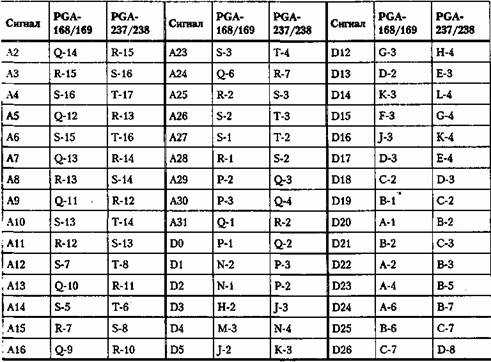

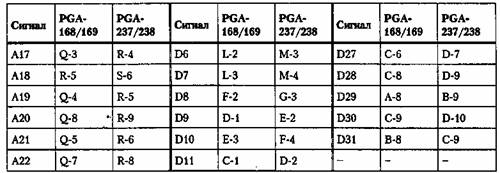

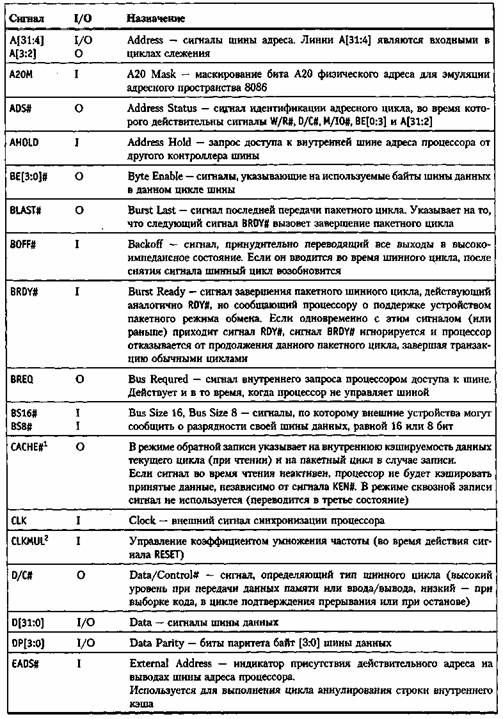

Таблица 2. Сигналы шин адреса и данных процессоров

486

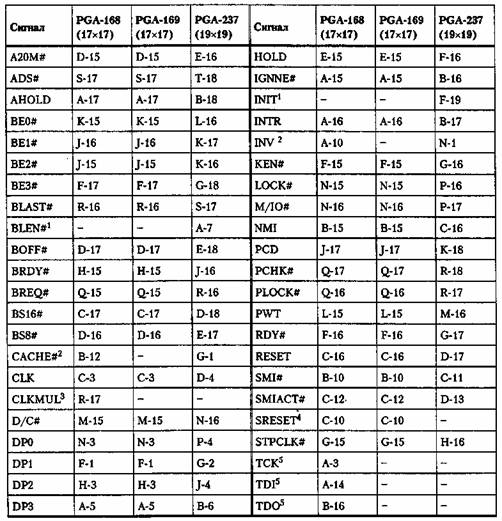

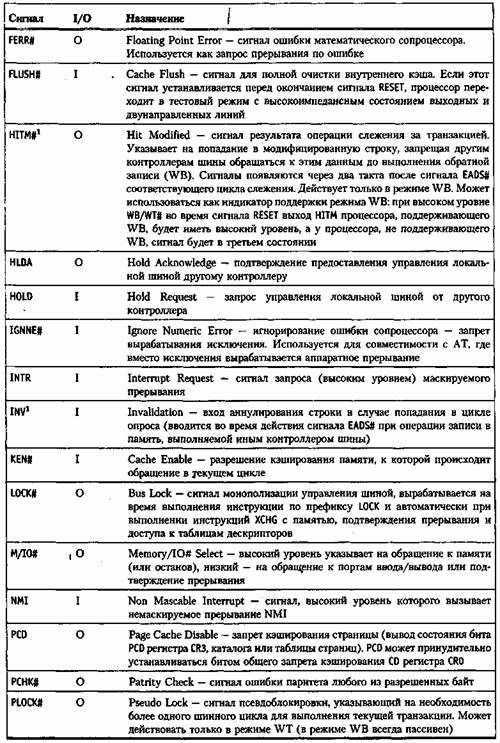

Таблица 3. Сигналы управления шины 486

1 Имеется только у Pentium OverDrive.

2 Имеется только у процессоров с WT-кэшем.

3 Имеется только у процессоров DX2 и DX4 AMD.

4 У процессора Pentium OverDrive

близким по назначению является сигнал INIT.3

Имеется только у процессоров, поддерживающих JTAG.

6 Сигнал UP является входным для процессоров в корпусе PGA-168 и выходным для остальных. ' Имеется только у

процессоров с пониженным питанием (3,3 В).

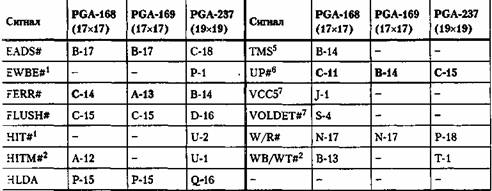

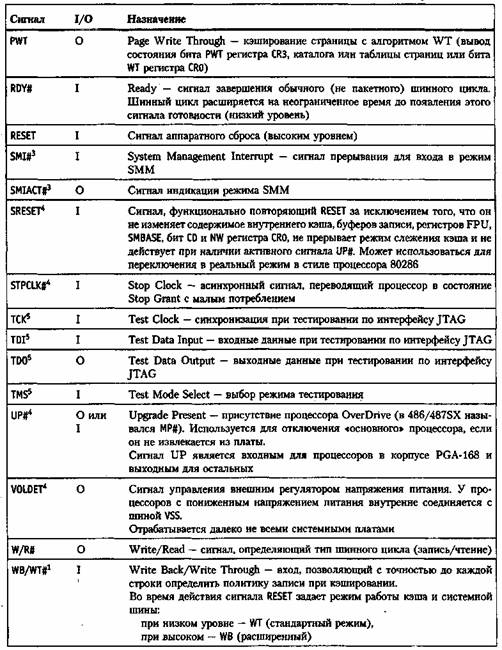

Таблица 4. Питание процессоров с шиной 486

*

Вывод К2 в сокете 237/238 выводами может соединяться с шиной 5 В через

резистор.

Напряжение

питания для большинства 486 процессоров Intel имеет номинал 5 В, кроме процессора DX4-100, который имеет напряжение питания 3,45 В, и

процессоров с маркировкой SL. В этом

плане от них выгодно отличаются процессоры AMD, в которых пониженное питание применяется в

большинстве моделей. Напряжение питания, если оно отличается от обычного,

указывается на процессоре.

Интерфейс

процессоров 486 похож на 386, но имеет некоторые новшества: пакетный режим

передачи, механизм аннулирования строк и очистки кэша, расширенный арбитраж,

контроль паритета данных и возможность 8-разрядного обмена. Для более поздних

версий процессоров, поддерживающих политику обратной записи первичного кэша, и

процессоров со средствами SMM и

управления энергопотреблением, имеются дополнительные сигналы. Назначение

сигналов раскрыто в табл. 5.

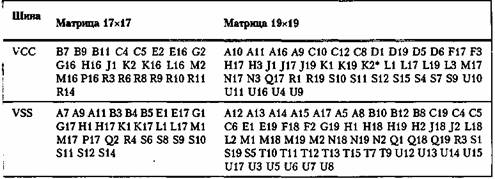

Таблица 5. Назначение сигналов процессора 486

1 Имеется только у процессоров с поддержкой WB-кэша.

2 Имеется только у процессоров с умножением частоты.

3 Имеется только у процессоров с поддержкой SMM.

4 Имеется не у всех процессоров.

5 Имеется только у процессоров с поддержкой интерфейса JTAG.

Синхронизация

процессора осуществляется внешним сигналом CLK, все временные параметры отсчитываются относительно

его положительного перепада. Внешняя тактовая частота процессором уже не делится

пополам (как у 386), а умножается на коэффициент, который у разных моделей

процессоров может принимать значение 1, 2, 2,5 и 3. При этом интерфейс внешней

шины процессора всегда работает на внешней частоте (Bus Frequency), а

частота тактирования вычислительного ядра (Core Frequency)

может повышаться в несколько раз. Стандартными значениями внешней частоты

являются 25, 33,33, 40 и 50 МГц. Коэффициент умножения задается уровнем

логического сигнала на входе CLKMUL Для

процессоров Ат5х86 высокий уровень (или неподключенный контакт) задает К=4,

низкий — К=3. Для процессоров Intel

DX4 и AMD DX4 высокий уровень (или неподключенный контакт) задает

К=3, низкий — К=2, для процессоров DX2

низкий уровень задает К=2. Этот сигнал используется только в процессорах DX2 и DX4, и на

системной плате обычно имеется джампер (или переключатель), задающий его

потенциал на контактах. Установкой джампера в соответствующее положение можно

выбрать требуемый коэффициент умножения, но, естественно, только в пределах

возможностей данного процессора: DX2

нельзя заставить работать на утроенной частоте.

Шина

адреса позволяет адресовать 4 Гбайт физической памяти (00000000-FFFFFFFFh) в защищенном режиме и 1 Мбайт из области младших

адресов — в реальном режиме. Сигналом А20М# можно включить принудительное

обнуление линии А20 (как для внутреннего кэша, так и для внешних операций).

Таким образом эмулируется циклический возврат адреса процессора 8086/88 (сигнал

воспринимается только в реальном режиме). При выполнении инструкций

ввода/вывода процессор адресуется к области в 64 Кбайт пространства

ввода/вывода (00000000-OOOOFFFFh).

Линии

А[31:2| идентифицируют адрес с точностью до двойного слова, а в пределах этого

слова сигналы ВЕ[0:3] непосредственно указывают, какие байты используются в

данном цикле. Линии А[31:4], определяющие адрес строки внутреннего кэша, в

циклах аннулирования работают на ввод.

Шина

данных D[31:0] допускает как 32-разрядный режим обмена, так и

16-и 8-раэрядный в зависимости от состояния входных сигналов BS16# и BS8#.

Сигналы BS16# или BS8# вводятся внешней схемой, если текущий цикл

адресуется к 16- или 8-битному устройству, подключенному к младшей части шины

данных, В58# имеет более высокий приоритет. Для связи с системной шиной,

имеющей возможность подключения 8-, 16- и 32-битных устройств (шины ISA и EISA) и полную

шину адреса, включающую сигналы АО, А1 и SBHE#, недостающие сигналы генерируются из сигналов

ВЕ[0:3]# по логике, приведенной на рис. 1. 8-битные устройства, наконец, могут

подключаться к шине данных без «косого» буфера.

Каждый

байт шины данных имеет бит паритета DP[3:0].

Схемы паритета генерируют корректные контрольные биты в циклах записи, а в

циклах чтения в случае ошибки паритета только вырабатывается сигнал ошибки на

выходе РСНК#, никак не влияющий на работу процессора. Он может использоваться

внешними схемами по усмотрению разработчика системной платы. Контроль четности

(количество единиц в байте вместе с битом паритета должно быть четным)

выполняется для всех байт, участвующих в конкретном цикле.

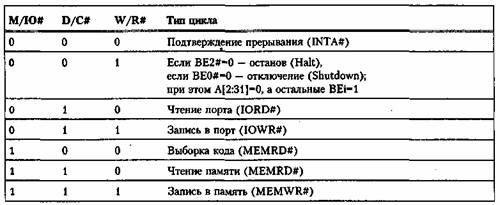

Тип

цикла локальной шины определяется сигналами M/IO#, D/CS, W/R#H LOCKS во

время активности сигнала ADSS (табл. 6).

Декодирование отличается от 386 положением специального цикла, который

перемещен из комбинации 101 в 001.

Таблица 6. Декодирование шинных циклов процессора 486

Для

управления шинными циклами процессор имеет входные сигналы готовности RDYS и BRDYS. Они

вырабатываются внешними схемами по их готовности к завершению шинного цикла

(как и для процессора 386). Сигнал BRDY# вырабатывают

устройства, поддерживающие пакетный режим обмена. На возможность пакетного

продолжения начатого цикла процессор указывает выходным сигналом BLASTS (при его низком уровне нет перспектив пакетного

продолжения).

На

необходимость блокировки циклов — защиты от захвата шины внешними контроллерами

— указывают выходные сигналы LOCKS и РLOCKS. Эти сигналы близки по назначению, но LOCKS защищает циклы типа «чтение-модификация-запись»

(которые должны защищаться безоговорочно для гарантии целостности данных), a PLOCKS

предохраняет от захвата шины, если текущий операнд не укладывается в один

шинный цикл (что важно для быстрой пересылки длинных операндов и заполнения

строк кэша).

Сигналы

арбитража локальной шины по сравнению с предыдущими процессорами дополнены

выходной линией BREQ, управляемой процессором в

любом состоянии. Этот сигнал указывает внешнему арбитру на то, что процессор

имеет внутренний запрос на использование шины. Сигнал устанавливается

одновременно со стробом ADSS. Если

процессор в данный момент не управляет шиной (по сигналу HOLD, AHOLD или BOFF), то сигнал появится в тот момент, когда процессор

выставил бы сигнал ADSS, если бы он управлял шиной.

Сигнал BREQ обеспечивает эффективный арбитраж в

многопроцессорных системах.

Для

запроса передачи управления локальной шиной другому устройству используется

сигнал HOLD. Когда процессор сочтет возможным передачу

управления (в незаблокированных циклах — сразу по завершении текущего шинного

цикла), он выставит сигнал подтверждения HLDA. Кроме того, имеется сигнал безусловного отключения

процессора от шины — BOFFS. По этому

сигналу процессор отдает управление шиной в следующем же такте, а текущий цикл

может

система

должна наблюдать за шиной, ожидая специального цикла подтверждения.

Сигналы

BLEN#, EWBE#, WB/WT#, INV воспринимаются процессором.

Сигнал

WB/WT#

воспринимается в каждом цикле обращения к памяти, позволяя определять политику

записи для каждой строки отдельно.

Сигнал

EADS# воспринимается только в состоянии HOLD, AHOLD или BOFF#.

Сигнал

PLOCK# не активен (постоянный высокий уровень).

Выбор

режима шины осуществляется процессором по состоянию линии WB/WT# в момент

окончания сигнала RESET, низкому уровню

соответствует стандартный режим шины (сквозная запись). Сигнал внутри

процессора резистором подтягивается к низкому уровню, так что на системной

плате, не поддерживающей режим обратной записи, у которой контакт В-13 (Т-1 в

сокетах 2 и 3) свободен, процессор всегда будет работать в стандартном режиме.

Сброс

и аппаратные прерывания процессора по интерфейсу аналогичны предыдущим

процессорам. Сигналы NMI и INTR высоким уровнем вызывают немаскируемое и маскируемые

прерывания. Сигнал RESET сбрасывает процессор в

исходное состояние, при его действии никакие другие входные сигналы, включая и HOLD, не воспринимаются. Если во время спада сигнала RESET удерживается высокий уровень на линии AHOLD, процессор выполнит внутренний тест BIST (Built-in Self Test). Дополнительный сигнал SRESET переводит процессор в исходное состояние, но с сохранением

состояния кэша, буферов записи, регистров FPU и некоторых бит других регистров.

Встроенный

математический сопроцессор — FPU — не

требует дополнительных сигналов для организации обмена данными, как это было в

прежних процессорах. Однако для обеспечения совместимости с архитектурой IBM PC, в

которой векторы прерываний, зарезервированные Intel под исключения процессора и сопроцессора,

традиционно используются для иных целей, процессоры 486DX имеют пару сигналов FERR# и IGNNE#. Сигнал

ошибки сопроцессора FERR#

аналогичен сигналу ERRORS сопроцессора 387 — он

вырабатывается в случае возникновения немаскированного исключения. Этот сигнал

в PC заводится на вход запроса IRQ13 вторичного контроллера прерываний. Входной сигнал IGNNE# заставляет сопроцессор игнорировать ошибки (не

вырабатывать внутренние исключения), при этом ошибка индицируется сигналом FERR# и может обрабатываться принятым в PC способом.

Процессор 486SX не может работать ни с каким

внешним сопроцессором (нет внешнего интерфейса). Как уже было сказано выше, при

установке «сопроцессора» 487SX существующий

«основной» процессор полностью отключается.